Power Master Semiconductor has released a new package portfolio, TO leadless (TOLL) package for 650V eSiC MOSFET series to meet the increasing demands for high power density and efficiency with superior switching performance in various applications such as AI data center servers, telecom infrastructure, flat panel display power, ESS, and battery formations.

Recently, the rapid growth of artificial intelligence (AI) is expected to drive continued strong data center demand. AI datacenters rely on GPUs that consume 10 to 15 times more power than traditional CPUs. SiC MOSFETs in TOLL package are an optimal solution for the rapidly expanding AI applications today.

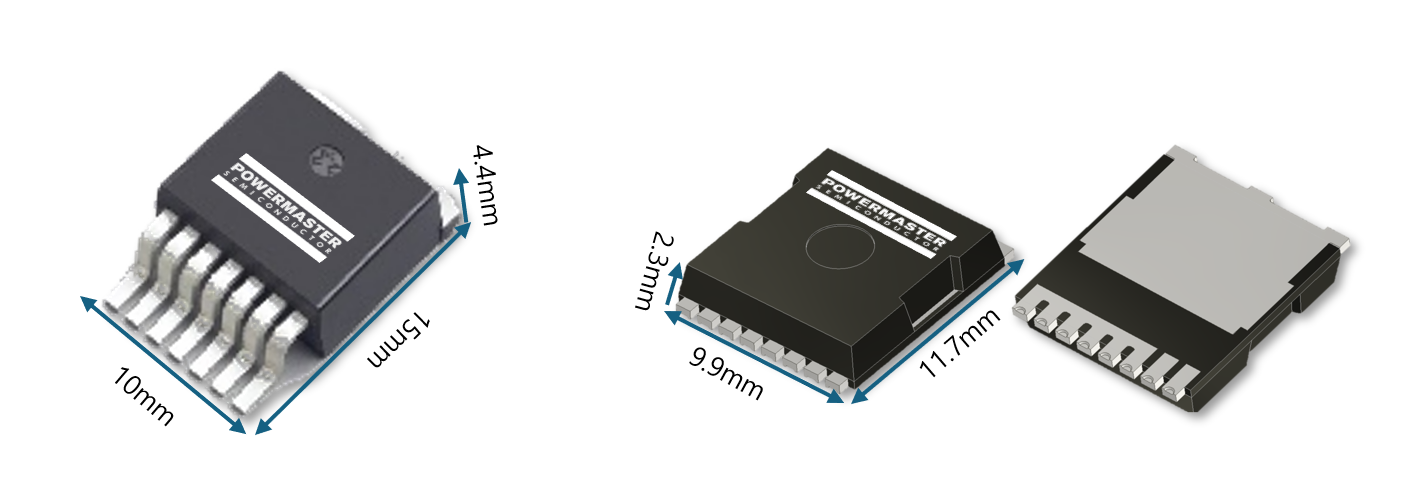

The TOLL package has a footprint of 9.9mm x 11.7mm, reducing the PCB area by 30% compared to the D2PAK 7-lead package. Moreover, with a thickness of 2.3mm, it has 60% less height than the D2PAK 7-lead package.

The TOLL offers superior thermal performance and low package inductance (2nH) compared to D2PAK 7-lead package. Kelvin source configuration lowers gate noise and reduces turn-on loss by 60% compared to same device without Kelvin source configuration, enabling higher frequency operation and improved power density. The new PCT65N27M1 has a VDSS rating of 650 V with a typical RDS(ON) of 27mΩ and a maximum drain current (ID) of 84 A.

Power Master Semiconductor’s products in TOLL package has special grooves in the gate and source pins to enhance the performance of the solder joint and offers Moisture Sensitivity Level 1 (MSL 1).

Original – Power Master Semiconductor