-

Transphorm, Inc. announced that its PCIM 2024 showcase will underscore its ability to outperform competitive wide bandgap technologies in higher power systems. For example, Transphorm’s normally-off d-mode SuperGaN®platform delivers higher electron mobility resulting in lower crossover losses versus Silicon Carbide—making it more a cost-effective, higher performing solution for various electric vehicle, datacenter/AI, infrastructure, renewable energy, and other broad industrial applications. To learn more, visit Transphorm during PCIM in Hall 7, Stall 108 during June 11 to 13, 2024.

Transphorm SuperGaN FETs are in production in a wide range of customer products crossing the power spectrum from low 45 W power adapters to higher power 7.5 kW PSUs. Many of these customer products are the first publicly recognized GaN-based systems of their kind and uniquely demonstrate advantages enabled only by the SuperGaN platform.

Examples include the previously mentioned liquid-cooled 7.5 kW PSU for mission-critical datacenter/blockchain applications; a 2.7 kW server CRPS with > 82 W/in3 power density (highest in any GaN power system available today); and 2.2 kW and 3 kW rack-mount 1U uninterruptible power supplies (UPSes). These design wins illustrate Transphorm’s ability to drive GaN into the various application markets composing an estimated GaN TAM of $8 billion by 2028.

In addition to real-world customer products, Transphorm continues to lead in technological achievements having recently demonstrated a 5 microsecond short-circuit withstand time, a bidirectional four-quadrant switch, and a 1200 V GaN-on-Sapphire device.

On-site demonstrations will include Transphorm solutions for 2- and 3-wheeler electric vehicle chargers along with customer PSUs for renewable energy systems, data centers, and more.

Speaking Engagement

Learn more about how Transphorm’s GaN solutions outperform competitive technologies and enable cross-industry innovations during the Bodo’s Power Systems session.

Panel: GaN Wide Bandgap Design, the Future of Power

Speaker: Philip Zuk, Senior Vice President, Business Development and Marketing

Date: June 12

Time: 2:20 – 3:20 p.m. CEST

Location: Hall 7, Stall 743Original – Transphorm

-

Applied Materials, Inc. reported results for its second quarter ended Apr. 28, 2024.

Applied generated revenue of $6.65 billion. On a GAAP basis, the company reported gross margin of 47.4 percent, operating income of $1.91 billion or 28.8 percent of net revenue, and earnings per share (EPS) of $2.06. On a non-GAAP basis, the company reported gross margin of 47.5 percent, operating income of $1.93 billion or 29.0 percent of net revenue, and EPS of $2.09.

The company generated $1.39 billion in cash from operations and distributed $1.09 billion to shareholders including $820 million in share repurchases and $266 million in dividends.

“Applied Materials continues to deliver strong performance in 2024, with fiscal second quarter revenue and earnings towards the high end of our guided range,” said Gary Dickerson, President and CEO.

“Applied Materials has the most enabling portfolio of materials engineering technologies for chips that underpin tectonic shifts in technology including AI, IoT, electric vehicles and clean energy, which puts us in a great position to grow along with these long-term, secular trends.”

Original – Applied Materials

-

Siltronic Portland proudly announced the inauguration of its state-of-the-art solar field on May 16, 2024. This marks a milestone in the company’s commitment to sustainability and reducing its carbon footprint.

“We see sustainability not just as a duty, but as a deeply rooted conviction. It is our responsibility not only to ensure financial profits, but also to work for the sustainable development of Siltronic and the preservation of our environment for future generations. Our new solar field exemplifies our commitment to a greener and more sustainable future”, stated Claudia Schmitt, CFO of Siltronic.

Siltronic AG has implemented a climate action plan aimed at limiting global warming to 1.5 degrees Celsius, in line with the 2015 Paris Climate Agreement. The company intends to reduce its Scope 1 and 2 greenhouse gas emissions by 42 percent by 2030, using 2021 as the baseline. Additionally, Siltronic aims to achieve net zero emissions by 2045. To achieve these targets, Siltronic utilizes three main levels: enhancing energy efficiency, generating its own renewable energy, and purchasing renewable energy.

As part of the in-house generation of renewable energy, the solar field with a capacity of 1,500 MWh per year started generating electricity last week. The energy produced from this solar field could sustain almost 140 Oregon households for an entire year. It contains 2,353 panels mounted on a fixed ground mount system and spans an area of 420 feet by 250 feet. The ribbon-cutting ceremony was conducted by Claudia Schmitt, CFO of Siltronic, and Subramania Krishnakumar, President of the Portland Site.

Founded in 1978 as Wacker Siltronic Corporation, the Portland site serves as the first international location in Siltronic’s production network. In 1980, the site celebrated the inauguration of Fab 1 and commenced production of 100 mm wafers, followed by expansions to increase capacity and capability, including the addition of 150 mm wafers in the mid-1980s. In 1996, production began in Fab 2, specializing in 200 mm wafers. Throughout its history, the Portland site has received numerous awards for its dedication to efficiency and sustainability. Today, Siltronic Portland remains focused on manufacturing high-quality 200 mm wafers for customers worldwide. With approximately 400 employees, the site specializes in wafering production, offering a range of polished and epitaxial wafers.

Original – Siltronic

-

LATEST NEWS2 Min Read

SemiQ will showcase its latest SiC power solutions and recently launched Known-Good-Die (KGD) screening process at PCIM Europe 2024 in Nuremberg from June 11-13, 2024.

During the event SemiQ will debut the latest addition to its QSiC™ family of high-speed-switching MOSFET half-bridge modules in S3 packages, which offer enhanced design flexibility and performance in current applications.

Featuring industry-standard 62mm footprints and standing at 26.3mm in height, the new power modules address the size, weight and power demands of challenging applications, ranging from induction heaters, welding equipment and uninterruptible power supplies (UPS) to photovoltaic and wind inverters, energy storage systems, high-voltage DC-DC converters and battery charging systems for electric vehicles (EVs). They are available in 600A (GCMX003A120S3B1-N) and 400A (GCMX005A120S3B1-N). Visitors will also be able to see SemiQ’s QSiC family of 1200V modules in SOT-227, half-bridge and full-bridge options.

Attendees visiting SemiQ’s stand at Alfatec’s booth (Hall 7, 418) will have the unique opportunity to learn more about the recently launched Known-Good-Die (KGD) screening program and see SemiQ’s MOSFET bare die on Known-Good-Die UV tape array for the first time. The KGD process delivers high-quality, electrically sorted and optically inspected advanced SiC MOSFET technology ready for back-end processing and direct die attachment.

“We’re thrilled to participate at PCIM, a significant event in the power electronics industry,” said Dr. Timothy Han, President of SemiQ. “With the expansion of our QSiC family, our goal is to offer a comprehensive, high-performance SiC portfolio across various sectors and offer customized solutions for cutting-edge designs. Our continued dedication to rigorous testing and quality assurance, delivering unmatched reliability, is embodied in our new KGD program which we will be demonstrating at the event.”

Founded in 1979, PCIM Europe stands as the pinnacle exhibition and conference for power electronics and its applications. Held annually in Nuremberg, the event attracts industry specialists and academia from around the globe, serving as the platform where new trends, technologies, and developments are first unveiled to the public.

Schedule a meeting with the SemiQ team right away using online calendar here or email at media@semiq.com.

Original – SemiQ

-

LATEST NEWS / PROJECTS2 Min Read

X-FAB Silicon Foundries SE, the leading analog/mixed-signal and specialty foundry, has updated its XP018 high-voltage CMOS semiconductor fabrication platform with new 40V and 60V high-voltage primitive devices, which feature an extended SOA for improved operational robustness.

These 2nd generation high-voltage primitive devices exhibit up to a 50% reduction in RDSon figures compared to the previous version. This offers an alternative which is better positioned to address certain key applications – particularly where devices’ footprints need to be reduced and unit costs minimized.

The XP018 platform is a modular 180nm high-voltage EPI technology solution, based on a low mask count 5V single-gate core module. It supports an extended temperature range of -40 to 175°C and offers a wide range of optional devices and modules, including high-gain bipolar devices, standard and high-capacitance MIM capacitors, multi-threshold (Vt) options, Schottky diodes, and depletion devices.

The platform is supported by high-reliability automotive NVM solutions, such as embedded Flash, EEPROM, and OTP, making it specifically designed for cost-sensitive and robust automotive, industrial, and medical applications.

In addition to the new 40V/60V devices, the platform has been enhanced by the inclusion of 5.3V Zener diodes. The new low leakage Zener diode is designed to effectively protect the gate oxide in critical applications, such as Wide Bandgap gate driver applications. Furthermore, there are also new isolated drain high-voltage devices up to 24V and a new 1.8 V medium Vt option on offer.

Tilman Metzger, Product Line Manager for High-Voltage at X-FAB, comments: “With this update of our XP018 platform we are demonstrating X-FAB’s commitment to enhancing established technologies. XP018 has been in production for more than a decade and still sees widespread adoption for new designs from our focus market segments: automotive, industrial and medical. The new competitive high-voltage devices and updates will enable our customers to implement more innovative and cost-effective products. Designers utilizing the new XP018 primitive devices have access to comprehensive PDK support across major EDA platforms like Cadence, Siemens EDA, Synopsys, ensuring seamless integration and optimization for a range of applications.”

A new medium Vt standard cell library is scheduled to be released in Q3 2024. Further details on the XP018 platform can be accessed by going to: www.xfab.com/technology/high-voltage

Original – X-FAB Silicon Foundries

-

LATEST NEWS / PRODUCT & TECHNOLOGY2 Min Read

DISCO Corporation has developed a process for diamond wafer manufacturing that applies the KABRA process, an ingot slicing method using laser technology. This process contributes to increasing the diameter of diamond wafers.

Diamond is often called the “ultimate semiconductor material” due to its superior material characteristics compared to Si, SiC, and GaN. In particular, as diamond has excellent insulation strength and heat conductivity, it is expected to be a good material for power semiconductors, and device development is underway at various research institutes.

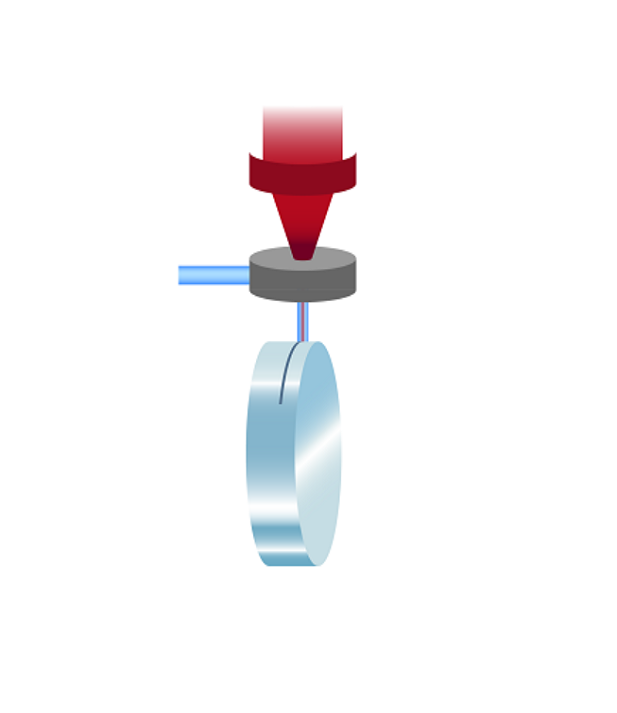

On the other hand, as it is an extraordinarily hard material, it came to be known that it is difficult to process mechanically. Therefore, laser became the general method used to slice wafers from a diamond crystalline ingot. However, with the conventional laser slicing method, as the ingot is processed from the sidewall, there was a limitation on the ingot diameter, and it was difficult to increase it.

With KABRA slicing, there is no limitation on the ingot diameter as the laser is irradiated from the upper surface of the ingot, making it possible to increase the ingot diameter.

Figure 1: Conventional slicing method using laser

Figure 2: KABRA for diamond processing

Features:

- Supports large-diameter ingots exceeding Φ50 mm

With the conventional method where the laser is irradiated from the sidewall of an ingot (Figure 1), the largest supported diameter was approx. Φ30 mm, but with the KABRA method (Figure 2), as the laser is irradiated from the upper surface of the ingot, there is no limitation on the ingot diameter. - Splitting wafers with a thickness of 100 µm or less is possible

By irradiating the laser at a shallow depth from the upper surface of the ingot, it is possible to split thin wafers. Therefore, a larger number of split wafers can be expected compared to the conventional method. - Achieves equivalent or higher throughput compared to the conventional method

The splitting speed is equal to or faster than the conventional method, achieving lower processing costs.

In addition, 45 patents related to this technology have been registered. Test cuts are available. Contact a DISCO sales representative.

Original – DISCO

- Supports large-diameter ingots exceeding Φ50 mm

-

LATEST NEWS3 Min Read

Alpha and Omega Semiconductor Limited (AOS) will showcase its expanding line of advanced power management solutions at PCIM 2024. Designed to meet the dynamic, important power management challenges in several key application areas and markets, the AOS products highlighted at PCIM include:

- New Silicon Carbide (SiC) MOSFET Announcement at PCIM: Supporting the needs of a wide range of automotive and industrial applications, AOS will introduce three new advanced package options for its latest Gen2 SiC MOSFET line. The new packages comprise a surface mount topside cooling option with a Kelvin source that meets the needs of the most power-dense advanced designs. It will also be announced that an AEC-Q101-qualified surface mount package will be in the standard D2PAK-7L footprint. The third package is a half-bridge module that provides an excellent solution for the high power industrial solar and charging station markets. The announcements will detail how these packages support AOS’ comprehensive line of SiC MOSFETs from 10mOhm to 500mOhm and voltages from 650V to 1700V.

- New Motor Drive Announcement at PCIM: AOS will announce a new range of 60V and 100V drivers for power tools, outdoor garden equipment, and e-mobility applications, including a 100V half bridge, a 100V 3-phase, and a 60V 3-phase. These products all support 100 percent duty cycle operation, and demo boards using AOS motor drivers and MOSFETs will be featured in the AOS booth.

- Power Supply and Renewable Energy: A significant solution in AOS’ growing High Voltage Super Junction MOSFET portfolio is its industry-leading optimized αMOS5™ 600V to 700V Super Junction MOSFETs that help designers achieve efficiency and density goals while satisfying budget goals. Featuring fast switching, a robust UIS/body diode, and ease of use, these state-of-the-art MOSFETs meet the latest server, telecom rectifier, solar inverter, EV charger, gaming, PC, and universal charging/PD design requirements. The newly released AONA66916, a 100V AlphaSGT™ MOSFET, delivers industry-leading Rthjc-top and Rthjc-bottom thermal resistances. A compact DFN 5×6 double-sided cooling package offers improved thermal designs in demanding telecom, solar, and DC-DC converter applications.

- Automotive and E-mobility: In AOS’ increasing line of automotive MOSFETs, the new automotive grade 80V (AOTL66810Q) and 100V (AOTL66912Q) MOSFETs in the TOLL package are designed to achieve the highest current capability. The AOS TOLL package utilizes advanced clip technology to achieve a high in-rush current rating and very low package resistance and inductance, enabling improved EMI performance compared to other TOLL packages based on standard wire-bonding technology packages. These new automotive-grade MOSFETs help designers meet the power requirements in electric vehicles, battery management systems (BMS), and high-performance inverters (BLDC motors) for e-mobility.

- Intelligent Power Modules, Mega IPM7: AOS has integrated its latest RC IGBT and high-voltage gate driver into the world’s most compact package design, capable of delivering mega power of up to 100W in motor control applications. The portfolio covers 600V / (1A−3A) in a variety of package options (Mega IPM-7D, IPM7DT, IPM-7E) that are ideal solutions for a broad array of design requirements.

- Poster Presentation: Jong-Mu Lee, Ph.D. and director of AOS IGBT and Module Product Lines, will present SiC-IPM for Compact and Energy Efficient in the Intelligent Power Modules session on Tuesday, June 11, at 15:30.

Original – Alpha and Omega Semiconductor

-

LATEST NEWS / PRODUCT & TECHNOLOGY / SiC / WBG1 Min Read

Taiwan Semiconductor – a global supplier of discrete power electronics devices, LED drivers, analog ICs and ESD protection devices – announced a family of 650V silicon carbide Schottky barrier diodes which are suitable for high-efficiency AC-DC, DC-DC and DC-AC conversion applications.

Unlike silicon-based fast-recovery rectifiers, these SiC devices have negligible switching losses due to low capacitive charge (QC). This makes them suitable for high-speed switching applications, benefitting circuit designs with increased power density and can reduce overall solution size.

Key Features

- Max. junction temperature 175°C

- High-speed switching

- High frequency operation

- Positive temperature coefficient on VF

- SPICE Models available

- Thermal Models available

Applications

- AD-DC conversion – PFC Boost

- DC-DC, Solar inverters

- Data center and server power

- Telecom – Datacom power

- UPS systems

Circuit Functions

- PFC boost diode

- Free-wheeling diode

- Full wave bridge

- Vienna bridgeless circuit

Original – Taiwan Semiconductor

-

Ideal Power Inc. reported results for its first quarter ended March 31, 2024.

“Commercial momentum continues as we commenced shipments of SymCool™ power modules to fulfill customer orders in the first quarter. We expect industrial markets, particularly the solid-state circuit breaker market served by our SymCool™ power module, to be the earliest source of our sales ramp,” said Dan Brdar, President and Chief Executive Officer of Ideal Power.

“In addition, all of our Phase II deliverables with Stellantis were successfully completed ahead of schedule and we added our first distributor, Richardson Electronics. They placed multiple orders with Ideal Power including an order from a company not previously in our sales funnel.”

Key First Quarter and Recent Business Highlights

Execution to B-TRAN™ commercial roadmap continues, including:

- Commenced commercial shipment of SymCool™ power modules to fulfill customer orders. The SymCool™ power module targets several applications including solid-state switchgear and circuit protection, renewable energy inverters for solar and wind, industrial inverters, hybrid and electric vehicles (“EVs”) and EV charging.

- Received an order for SymCool™ power modules and drivers from one of the two Forbes Global 500 leaders in diverse power management markets in Ideal Power’s B-TRAN™ test and evaluation program. This global power management market leader is evaluating SymCool™ against IGBT modules for use in solid-state circuit breaker (“SSCB”) applications.

- Received an order for B-TRAN™ devices and a circuit breaker evaluation board from a global leader in power semiconductor and power electronics solutions in connection with its launch of a multi-year DC power distribution system program. This global leader presents multiple opportunities as it addresses several of our target industrial markets: SSCBs, industrial and grid infrastructure and renewable energy.

- Successfully completed Phase II of a product development program with Stellantis, a top 10 global automaker. All Phase II deliverables were completed ahead of schedule including a wafer run and deliveries of tested B-TRAN™ devices, drivers and a Stellantis approved comprehensive reliability test plan for automotive qualification. Ideal Power is partnering with Stellantis’ advanced technology development team to develop a custom B-TRAN™ power module for use in EV drivetrain inverters in Stellantis’ next generation EV platform.

- Added the first distributor, Richardson Electronics, for discrete B-TRAN™ device and SymCool™ power modules. Richardson Electronics placed multiple orders with Ideal Power including an order from a company not previously in Ideal Power’s sales funnel.

- Added a global leader in circuit protection, industrial fuses and power conversion technology with over a billion in annual sales to the roster of the B-TRAN™ test and evaluation program.

- Released B-TRAN™ and SymCool™ videos and application notes for the technical audience at prospective customers, resulting in the addition of new opportunities to the sales funnel. The videos demonstrate the testing of discrete B-TRAN™ devices and SymCool™ power modules and the compelling advantages B-TRAN™ offers to SSCB applications.

- Nearing completion of a qualification run with the second high-volume wafer fabrication partner. This wafer fab in Europe will support future revenue growth and add dual sourcing for wafer fabrication.

- B-TRAN™ Patent Estate: Currently at 86 issued B-TRAN™ patents with 39 of those issued outside of the United States and 41 pending B-TRAN™ patents. Current geographic coverage includes North America, China, Japan, South Korea, India, and Europe, with pending coverage in Taiwan.

First Quarter 2024 Financial Results

- Completed a public offering, raising net proceeds of $15.7 million. The initial closing in late March resulted in net proceeds of $13.7 million and the exercise of the underwriter’s overallotment option in April resulted in additional net proceeds of $2.0 million.

- Commercial revenue increased to $78,739 in the first quarter of 2024 from $0 in the first quarter of 2023.

- Operating expenses in the first quarter of 2024 were $2.5 million compared to $2.6 million in the first quarter of 2023.

- Net loss in the first quarter of 2024 was $2.5 million compared to $2.5 million in the first quarter of 2023.

- Cash used in operating, investing and financing activities in the first quarter of 2024, excluding the net proceeds from the public offering, was $1.9 million compared to $1.8 million in the first quarter of 2023 and down from $2.3 million in the fourth quarter of 2023.

- Cash and cash equivalents totaled $20.2 million at March 31, 2024.

- No long-term debt was outstanding at March 31, 2024.

2024 Milestones

For 2024, the Company has set or achieved the following milestones:

- Successfully completed Phase II of development program with Stellantis

- Secure Phase III of development program with Stellantis

- Complete qualification of second high-volume production fab

- Convert large OEMs in test and evaluation program to design wins/custom development agreements

- Add distributors for SymCool™ products

- Initial sales of SymCool™ IQ intelligent power module

- Begin third-party automotive qualification testing

Original – Ideal Power