-

LATEST NEWS / SiC / WBG2 Min Read

SemiQ has opened its newest office in Taiwan. This strategic move underscores SemiQ’s commitment to providing enhanced ground support to its valued customers in the region while further solidifying its presence in the Asia-Pacific market.

As a Product Engineering and Global Sourcing Center, the new office, located near the Taiwan High Speed Rail Hsinchu Station, will serve as a vital hub, facilitating seamless interfacing with key stakeholders including Hsinchu Foundry, Miaoli Test Facility, Far East OSATs, and Taiwan Sales Office.

“Expanding our presence in Taiwan represents a significant milestone for SemiQ as we continue to strengthen our global operations and better serve our customers,” said Michael Tsang, VP, Product Engineering and Operations at SemiQ. “The opening of this office underscores our dedication to providing unparalleled support and resources to our customer base in the region.”

Mr. Tsang, a seasoned professional with extensive experience in semiconductor industry dynamics, will lead the Taiwan office. His expertise will be instrumental in managing demand, fostering partnerships, and ensuring the highest level of service delivery to SemiQ’s customers.

The strategic location of the new office near key industry players and transportation hubs will enhance SemiQ’s ability to collaborate effectively with its partners, streamline operations and expedite response times to customer needs.

“We are excited about the opportunities that the Taiwan office brings in terms of strengthening relationships with our partners and better understanding the evolving needs of the market,” added Mr. Tsang. “This expansion aligns with our vision of driving innovation and delivering value-added solutions to our customers.”

Establishing the Taiwan office complements SemiQ’s existing wafer processing facilities in the region. It underscores its commitment to providing superior SiC solutions for ultra-efficient, high-performance, and high-voltage applications.

Original – SemiQ

-

LATEST NEWS / SiC / WBG2 Min Read

Axcelis Technologies, Inc. announced a shipment of the Company’s Purion EXE™ SiC high energy implanter as well as a successful Purion H200™ SiC medium energy implanter evaluation closure at leading power device chipmakers located in Japan. The systems will be used for 150mm and 200mm production of silicon carbide power devices supporting automotive, industrial, energy, and other power intensive applications.

Greg Redinbo, Executive Vice President, Marketing and Applications remarked, “The successful evaluation closure of the 200mm Purion H200 SiC system enables it to join an existing 200mm Purion EXE SiC in production at a leading power device customer in Japan.” Dr. Redinbo continued, “The shipment of an additional Purion EXE SiC to a new 150mm customer in Japan highlights growing customer requirements for even higher energy ion implant recipes on advanced SiC power devices, which the Purion Power Series provides.”

President and CEO, Russell Low commented, “We look forward to supporting our growing installed base in Japan and remain focused on expanding our market share by providing customers with the most innovative implant technology and support solutions to ensure their success. The Purion Power Series is the market leader due to its highly differentiated features and process control capabilities that are enabling for power device applications. Axcelis is the only ion implant company that can deliver complete recipe coverage for all power device applications.”

Original – Axcelis Technologies

-

LATEST NEWS / SiC / WBG4 Min Read

Aehr Test Systems announced it has received an initial customer order for a FOX-NP™ wafer level test and burn-in system, multiple WaferPak™ Contactors, and a FOX WaferPak Aligner to be used for engineering, qualification, and small lot production wafer level test and burn-in of their silicon carbide devices.

The customer is multiple billion dollar per year global semiconductor company with locations across Europe, Asia, and the Americas that serves various industries including automotive, industrial, mobile, and consumer applications. The FOX-NP system, including the FOX WaferPak Aligner and initial WaferPaks, are scheduled to ship over the next few months.

The FOX-NP system is configured with the new Bipolar Voltage Channel Module (BVCM) and Very High Voltage Channel Module (VHVCM) options that enable new advanced test and burn-in capabilities for silicon carbide power semiconductors using Aehr’s proprietary WaferPak full wafer Contactors.

Gayn Erickson, President and CEO of Aehr Test Systems, commented, “We are very excited that this new customer selected our FOX-P solution for engineering, qualification, and production of their silicon carbide power devices. After working with the Aehr team and our technology solutions over an extended period of time, they felt secure in our ability to aid them in achieving these goals. A key feature in their selection of our FOX solution is its proven ability to cost-effectively implement their target burn-in and stabilization requirements, including 100% traceability and proof that every device on the wafer is burned in for the needed test duration.

“This customer currently has a wide range of automotive products and is entering the silicon carbide market to address several applications that include automotive, industrial, and electrification infrastructure. Key capabilities of our solution include our ability to scale from engineering and qualification and small lot production with the FOX-NP system to large scale production with the FOX-XP with Automated WaferPak Aligner. They have told us that they plan to transition to our FOX-XP multi-wafer test and burn-in systems for high-volume production. Aehr’s FOX-P technology facilitates a seamless transition from engineering to high-volume production with 100% compatibility between systems.

“This customer sees the enormous opportunity for silicon carbide power devices in industrial and power applications. William Blair forecasts that in addition to the 4.5 million six-inch equivalent wafers that will be needed to meet the demand for electric vehicle related silicon carbide devices in 2030, another 2.8 million wafers are needed to address industrial, solar, electric trains, energy conversion and other applications in 2030. The cost of ownership of our solution proves to be more cost-effective and efficient for these devices than package part burn-in after the die are packaged. This is a strong testimony of the advantage of wafer level burn-in as a better alternative to package part burn-in.

“The FOX family of compatible systems including the FOX-NP and FOX-XP multi-wafer test and burn-in systems and Aehr’s proprietary WaferPak full wafer contactors provide a uniquely cost-effective solution for burning in multiple wafers of devices at a single time to remove early life failures of silicon carbide devices, which is critical to meeting the initial quality and long-term reliability of the automotive, industrial, and electrification infrastructure industry needs.”

The FOX-XP and FOX-NP systems, available with multiple WaferPak Contactors (full wafer test) or multiple DiePakTM Carriers (singulated die/module test) configurations, are capable of functional test and burn-in/cycling of devices such as silicon carbide and gallium nitride power semiconductors, silicon photonics as well as other optical devices, 2D and 3D sensors, flash memories, magnetic sensors, microcontrollers, and other leading-edge ICs in either wafer form factor, before they are assembled into single or multi-die stacked packages, or in singulated die or module form factor.

Original – Aehr Test Systems

-

INDUSTRY PAPERS33 Min Read

Abstract

The silicon carbide (SiC) inverter brings great advantages to the motor drive systems of new energy vehicles; however, severe challenges to the bearings also happen. The high dc bus voltage and switching frequency of SiC inverter can increase the discharge frequency and energy when the bearing grease film collapses.

As a result, the bearing suffers severe electric corrosion, and the service life of the motor drive system can be shortened. In this paper, the characteristics of common-mode voltage and bearing voltage are analyzed, firstly under space vector pulse width modulation (SVPWM). After that, the common-mode equivalent circuit model of the motor drive system is established. The frequency characteristics of bearing voltage are revealed, and the safe working area is determined.

Then, the frequency characteristics of bearing voltage and current are verified based on IGBT and SiC inverters in experiments. After that, by designing a common-mode filter, the bearing voltage and current are significantly attenuated. Furthermore, the active zero state PWM (AZSPWM) is adopted to reduce the common-mode voltage from the inverter.

At the same time, combined with the common-mode filter, the bearing voltage and current are further reduced. The experimental results show that the switching frequency has a decisive effect on the amplitude of bearing voltage and current. The bearing voltage can be attenuated to around half of the reference bearing voltage by using the common-mode filter and AZSPWM strategy, respectively. T

he combination of the common-mode filter and AZSPWM strategy can reduce the bearing voltage to around one-fourth of the reference bearing voltage, which can effectively reduce the breakdown time and discharge energy of the grease oil film.

1. Introduction

The bearing is the key component which determines the life and reliability of the motor drive system. Motor failures are largely attributed to damage to the bearing, and electric corrosion is one of the main factors. Considering the complexity and cost, the three-phase, two-level voltage source inverter is mainly adopted in the electric vehicle drive system.

The common-mode voltage of the inverter couples through the parasitic capacitances of the motor, resulting in bearing voltage on both sides of the bearing lubricating grease oil film. When the bearing voltage exceeds the breakdown threshold of the lubricating grease oil film, the discharge phenomenon occurs, leading to the electric discharge machining (EDM) bearing current.

The energy released during the discharge can cause concave pits on the surface of inner and outer rings as well as on the rolling balls of the bearing. A large number of breakdown discharges can cause great damage to the bearing, posing a serious threat to the life of the motor drive system.

The 800 V dc bus voltage and SiC power devices are becoming the development direction for electric vehicle drive systems. The high voltage and high frequency are conducive to the reduction in the volume and the improvement of the power density of motor drive systems. For example, in 2022, Marelli Europe S.p.A., a well-known auto parts supplier, developed a high power density SiC inverter with a dc bus voltage of 900 V and a switching frequency of 65 kHz.

Compared with the traditional IGBT inverters, its volume and weight were reduced by 30%, the loss was reduced by 50%, and the efficiency reached 99.5%. The National New Energy Vehicle Technology Innovation Center also developed an SiC inverter with a dc bus voltage 900 V in 2022, with the capacity of 550 kVA and a switching frequency of 25 kHz. Compared with the traditional design, the volume was reduced by 6.6 times, and the weight was reduced by 3.3 times.

However, the increase in dc bus voltage and switching frequency could exacerbate the bearing electric corrosion. Bearing electric corrosion has become a pain point problem that needs to be solved urgently in the field of electric vehicles.

From current research, it could be summarized that the suppression of the motor bearing current can be addressed from three aspects, including the bearing reinforcement, the capacitive coupling paths within the motor, and the source of common-mode voltage. Conductive grease bearings and ceramic bearings have been applied to suppress bearing current. Conductive grease bearings create a conductive channel inside the bearing, bypassing the bearing oil film, making it difficult to establish a stable bearing voltage, which prevents the discharge of the bearing oil film.

However, the metallic particles in the lubricating grease can increase its mechanical wear. Additionally, designing a lubricating grease that balances both lubrication and conductivity poses a technical challenge. Ceramic bearings employ the insulating method to block the current path, increasing the bearing impedance to suppress the bearing current. However, the ceramic bearing can impact the rotor heat dissipation.

Additionally, the accumulated bearing voltage on the shaft still exists, which can create a coupling loop through the non-insulated bearing or gear system of the reducer, still leading to electric corrosion. Ceramic bearings are generally used with the conductive brush to obtain better suppression effect. The conductive brush can release the bearing voltage as much as possible to the housing through a low-impedance path. However, ceramic bearings are relatively expensive, and the conductive brushes require regular maintenance and replacement.

From the perspective of the capacitive coupling paths, it can diminish the capacitive coupling effect to reduce bearing voltage by optimizing the motor design. Additionally, a grounded electromagnetic shielding layer is installed at the end of the stator windings to alter the parasitic capacitive coupling path, thereby suppressing the bearing currents.

However, the suppression effect of bearing currents is relatively small through optimizing windings and slot shapes. Moreover, the electromagnetic shielding layer increases the manufacturing difficulty and the motor cost. The eddy current effect inside the shielding layer leads to an increased temperature, thus reducing its practical application in the industrial field.

The root cause of bearing current lies in the common-mode voltage of the inverter. The amplitude and frequency of the common-mode voltage directly determine the severity of bearing currents. Therefore, by reducing the amplitude of the common-mode voltage at its source, the pressure on bearing design can be significantly alleviated.

The suppression of common-mode voltage can be achieved through both software and hardware methods. Software methods involve the utilization of non-zero vectors modulation strategies, such as AZSPWM, remote-state PWM (RSPWM), near-state PWM (NSPWM), etc. Non-zero vector modulation strategies can reduce the amplitude of common-mode voltage to one-third of that in traditional SVPWM.

The hardware suppression methods mainly include innovative inverter structures, such as multi-level and multi-phase topology circuits, etc. These topologies provide a higher degree of design freedom and can effectively reduce the common-mode voltage when combined with specific modulation strategies. However, considering all factors, including the cost, the power density, and the complexity, the multi-phase and multi-level topologies are less commonly applied in electric vehicles. In addition, the passive filters can also be used to suppress bearing currents thanks to the simple structure.

Unlike IGBT inverters, the SiC inverters have a unique impact on bearing voltage and bearing current. Currently, few studies on motor bearing current under an SiC inverter are available. The high-frequency characteristics of the SiC inverter are more likely to excite parasitic capacitances within the motor, causing complex effects on bearing voltage and bearing current. Moreover, the mechanisms of the bearing voltage and bearing current are not clear, and urgent studies are needed.

This paper aims to reveal the frequency characteristics of bearing voltage and bearing current, and to propose an effective suppression method. In this paper, the characteristics of bearing voltage and bearing current are studied by using IGBT and SiC inverters.

The common-mode equivalent circuit of a motor drive system is established, and the frequency–characteristic curve of bearing voltage is obtained. The principle of dividing the anger zone and safe operating zone of bearing voltage is obtained. The common-mode filter and AZSPWM strategy are adopted to suppress the bearing voltage.

This paper is organized as follows. Section 2 presents the generation mechanism and coupling path of bearing voltage and bearing current. Section 3 presents the high-frequency common-mode equivalent circuit of the motor drive system and the concept of the safe operating zone for bearing voltage. Section 4 describes the experimental platform and test results based on IGBT and SiC inverters. Section 5 presents a suppression method of a common-mode filter to suppress the bearing current. Section 6 presents a suppression method of combining the AZSPWM strategy with the common-mode filter. Section 7 concludes the paper.

2. Bearing Voltage and Bearing Current in Motor Drive System

2.1. Generation Mechanism and Coupling Path

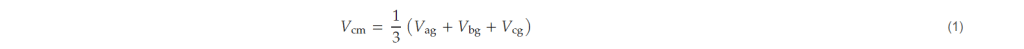

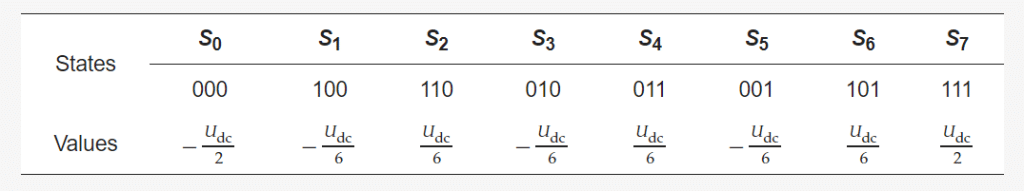

The source of the bearing voltage and bearing current is the high-frequency common-mode voltage output by the inverter. As shown in Figure 1, a three-phase, two-level voltage source inverter comprises of six switch devices, and the common-mode voltage of the inverter Vcm is shown as Equation (1). Vag, Vbg, and Vcg are the three-phase voltages of the inverter to the reference ground g (the inverter heatsink and the motor housing).

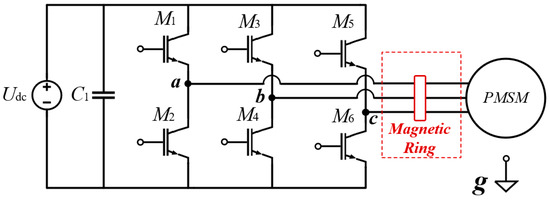

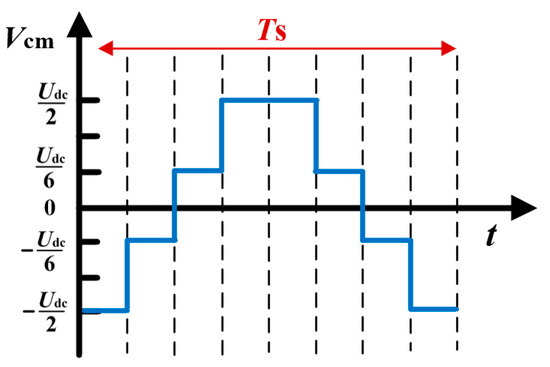

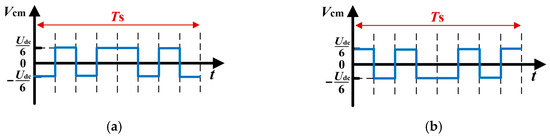

There are eight switch states for the inverter under the SVPWM strategy. The numbers 0 and 1 are utilized to denote the switch states of a bridge arm in an inverter. The state of 1 indicates that the upper device is closed while the lower device is open. The state of 0 indicates that the upper device is open while the lower device is closed. Consequently, the Vcm values of eight switch states are shown in Table 1, while the waveform of Vcm is shown in Figure 2.

In Figure 2, the Udc represents the dc bus voltage and the Ts represents the time of a switching cycle. The common-mode voltage Vcm is a four-level waveform under the SVPWM strategy. In this paper, the impact of switching frequency fs on the common-mode voltage Vcm and bearing voltage Vb is analyzed.

Figure 1. Schematic diagram of the motor drive system.

Figure 2. Waveform of common-mode voltage Vcm under SVPWM strategy.

Table 1. Common-mode voltage of the inverter under 8 switch states by using the SVPWM strategy.

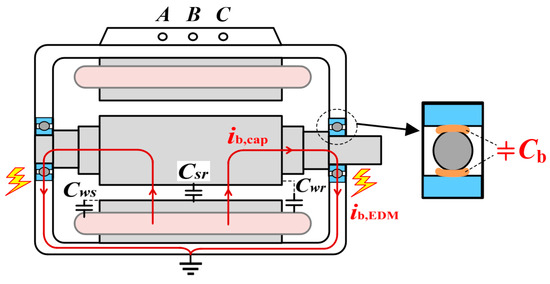

Under the excitation of high-frequency common-mode voltage, the impedance state of the motor exhibits a capacitive characteristic. As shown in Figure 3, Cws, Cwr, and Csr represent the parasitic capacitances of the winding to the stator core and to the rotor, and the stator core to the rotor, respectively. Cb represents the equivalent capacitance of the bearing grease oil film. These parasitic capacitances provide a low impedance coupling path for the high-frequency common-mode voltage.

Figure 3. High-frequency parasitic capacitances inside the motor.

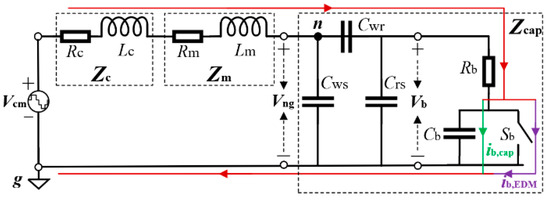

The generation process of bearing voltage and bearing current can be described by the equivalent circuit shown in Figure 4. The n point represents the neutral point in the star-connected motor. Vcm represents the common-mode voltage output from the inverter, and Vng represents the common-mode voltage at the motor neutral point. Lc and Rc are the equivalent common-mode inductance and resistance of the cable, respectively, and Lm and Rm are the equivalent common-mode inductance and resistance of the motor winding, respectively. The Rb is the equivalent resistance of the bearing, and Sb is the analog switch in the circuit.

After passing through the cable and the motor winding, Vcm generates Vng at the neutral point of the motor. Under the coupling effect of parasitic capacitances in the motor, a stable bearing voltage Vb is formed at both ends of the bearing lubricating grease film. At this time, the switch Sb in Figure 4 is open, and the change in bearing voltage regularly charges and discharges the oil film capacitance Cb to form the dv/dt capacitive bearing current ib,cap. The amplitude of ib,cap is small, and its influence on bearing electric corrosion is generally ignored.

When the Vb exceeds the voltage threshold of the lubricating grease oil film, the discharge phenomenon occurs. At the discharge moment, the oil film is no longer stable and the Vb drops to 0 V. At this time, the analog switch Sb in Figure 4 is closed, and Cb is shorted to simulate the breakdown and discharge process of the oil film.

The bearing current generated by the discharge is called EDM bearing current ib,EDM. The amplitude of ib,EDM is large, and the energy is released instantaneously. The heat released by multiple discharges could melt the rolling elements and raceways, which is the most direct cause of bearing electric corrosion. According to the above analysis, although the coupling paths of ib,cap and ib,EDM are the same, they do not occur simultaneously.

Figure 4. Common-mode equivalent circuit of a motor drive system.

2.2. Analytical Calculation Process

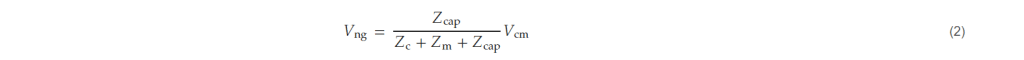

According to the common-mode equivalent circuit shown in Figure 4, the Vng is obtained as shown in Equation (2). Zc is the equivalent common-mode impedance of the cable, Zm the equivalent common-mode impedance of the motor winding, and Zcap is the common-mode impedance of parasitic capacitances inside the motor.

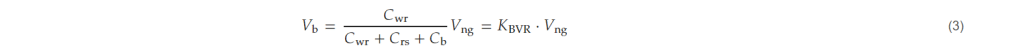

Ignoring the bearing resistance Rb, which is generally very small, the relationship between Vb and Vng is shown in Equation (3). KBVR is defined as the bearing partial pressure ratio, which is often used to roughly evaluate the electric corrosion degree of the bearing. When the bearing is in a stable rotating state, the bearing oil film thickness is stable. Cb is a constant value and KBVR can be considered as a constant.

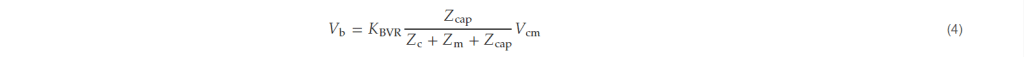

According to Equations (2) and (3), the relationship between Vb and Vcm is shown in Equation (4). Vb is the result of the voltage division of Vcm through a common-mode equivalent circuit, and the waveform of Vb is consistent with those of Vcm and Vng, both of which are four-level waveforms. When the amplitude and frequency of Vcm are determined, Vb is decided by the common-mode impedances of the cable and motor, which in turn determines the magnitude of ib,EDM.

The accurate calculation of ib,EDM is very difficult, as it depends on the bearing voltage and the impedance of the bearing lubricating grease oil film. The thickness of bearing oil film highly depends on its speed, load, temperature, and the raceway surface roughness. During the rotation process, the lubricating grease oil film is uneven. When the bearing voltage exceeds the voltage threshold, the oil film would break down and discharge at its weakest position.

Therefore, the occurrence of the ib,EDM can be regarded as irregular, and some studies believe that it is random, following statistical probability. However, it should be noted that the occurrence probability of ib,EDM depends on the stable amplitude of the Vb and increases with the increase in Vb.

3. Analysis Model of a Common-Mode Equivalent Circuit for Bearing Voltage

3.1. Frequency Characteristics Analysis of Bearing Voltage

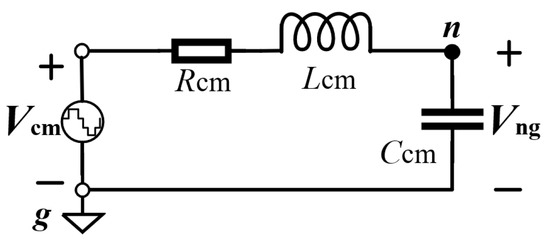

According to Equation (4), when Vcm is determined, the Vb and ib,EDM are mainly affected by the common-mode impedance of the cable and motor. Therefore, it is necessary to study the frequency characteristics of the common-mode impedance of the motor. The common-mode equivalent circuit in Figure 4 is simplified as shown in Figure 5, where Rcm, Lcm, and Ccm are the equivalent resistance, the inductance, and capacitance of the simplified common-mode circuit, respectively.

Figure 5. Simplified common-mode equivalent circuit of a motor drive system.

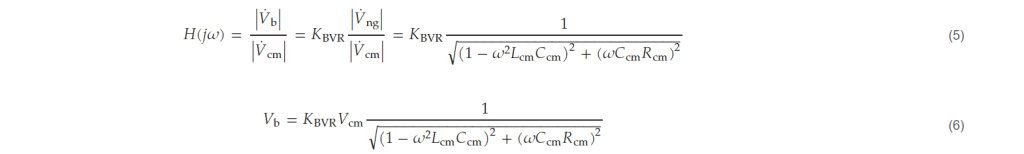

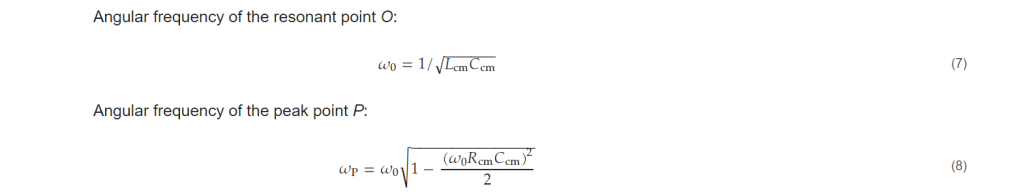

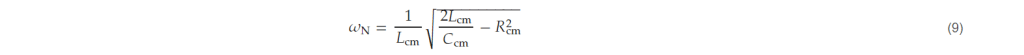

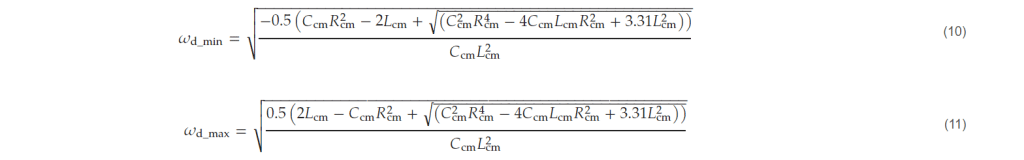

Based on the RLC series equivalent circuit in Figure 5, the variation law of Vng can be obtained by analyzing the voltage frequency characteristics of Ccm. According to Equation (3), the voltage frequency characteristics of Vb are consistent with Vng, so the amplitude–frequency characteristics of Vb can be obtained, as shown in Equation (5).

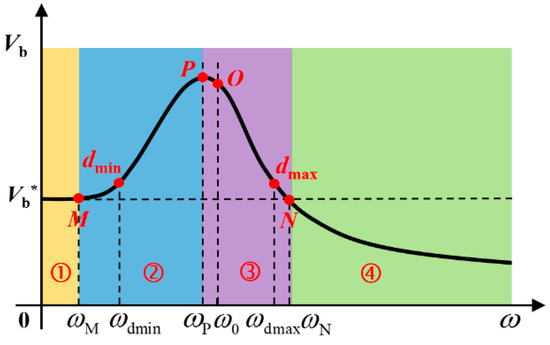

After the dc bus voltage of the inverter is determined, the Vcm amplitude is determined and the relationship between the Vb and frequency is obtained, as shown in Equation (6). The corresponding frequency–characteristic curve is shown in Figure 6. The P denotes the peak point, and the O denotes the resonant point of the curve in Figure 6. The ωP and ω0 are angular frequencies at points P and O, respectively.

Figure 6. Frequency–characteristic curve of bearing voltage Vb.

In zone ① in Figure 6, the amplitude of Vb remains basically unchanged, and the Vb in this zone is defined as the reference bearing voltage Vb*. The point N is defined as the bearing voltage attenuation point, and the corresponding amplitude is also Vb*. The angular frequency ωN of point N is obtained as follows:

3.2. The Danger Zone and Safe Operating Zone of Bearing Electric Corrosion

As illustrated in Figure 6, the variation trend of Vb is associated with the system common-mode impedance parameters and switching frequency. With the increase in switching frequency, the amplitude of Vb shows a trend of first rising and then decreasing. The frequency–characteristic curve in Figure 6 is divided into four zones. The analysis of each zone is as follows:(1)

Zone ①: the frequency of common-mode excitation is before the ωM. With the increase in frequency, the amplitude of Vb increases slowly and the frequency dependence of Vb is low. This zone is defined as the bearing voltage stable zone. There is Vb ≈ Vb* in this region. The Vb is usually in this zone when the motor is driven by an IGBT inverter (typical switching frequency between 2 kHz and 8 kHz).(2)

Zone ②: the frequency of common-mode excitation is between ωM and ωP, and the amplitude of Vb increases significantly with the increase in frequency. This zone is defined as the bearing voltage growth zone. In this zone, there is always Vb > Vb*, and the Vb reaches its peak value at point P.(3)

Zone ③: the frequency of common-mode excitation is between ωP and ωN, and the amplitude of Vb decreases gradually with the increase in frequency. This zone is defined as the bearing voltage drop zone. In this zone, there is always Vb > Vb*, and Vb decreases to Vb* at point N. However, the amplitude of Vb is still large in this zone.(4)

Zone ④: when the frequency of common-mode excitation exceeds the ωN, Vb begins to decrease below Vb*, and the rate of decline gradually slows down with the increase in frequency. This zone is defined as the bearing voltage safety attenuation zone. In order to reduce the risk of bearing electric corrosion, it is hoped that the switching frequency of the inverter is located in this zone.

In order to better evaluate the impact of bearing voltage on bearing electric corrosion, the zone in Figure 6 where Vb ≥ 1.1 Vb* is defined as the bearing electric corrosion danger zone. According to Equation (6), the expressions of ωd_min and ωd_max of, respectively, the lower and upper frequency points in this zone are as follows:

In order to avoid the risk of bearing corrosion, the selection of switching frequency should try to avoid the danger zone between dmin and dmax in Figure 6. However, the selection of switching frequency is determined by many factors, such as efficiency, volume, power density, electromagnetic interference performance, etc. Therefore, the curve in Figure 6 can provide some references for the selection of the switching frequencies of SiC inverters.

Compared with other zones, zone ④ can obtain a smaller amplitude of Vb. Driven by a traditional IGBT inverter, Vb is often in region ①. However, the SiC device increases the switching frequency of the inverter, causing Vb to be located in zones ② or ③ with a large amplitude. This will increase the frequency and the harm degree of the EDM bearing current, causing serious bearing electric corrosion.

4. Experimental Measurement of Bearing Voltage and Bearing Current

4.1. Experimental Platform and Measurement Methods

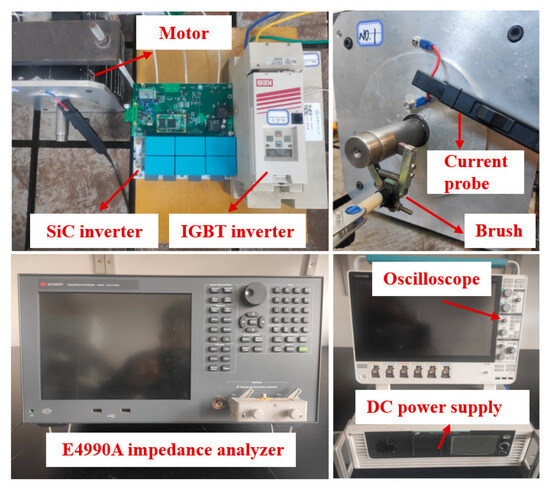

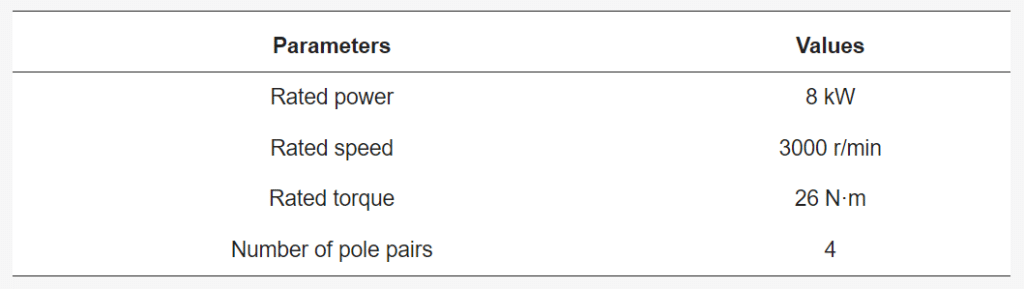

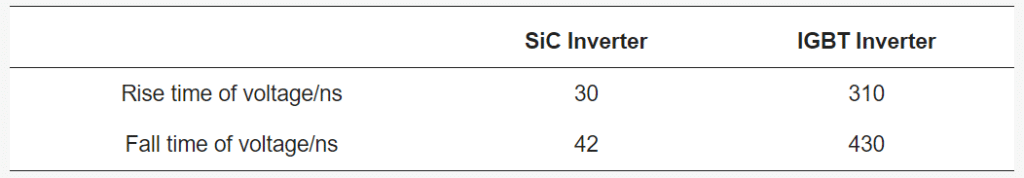

The experimental platform is established as shown in Figure 7. An embedded permanent magnet synchronous motor is adopted with 6007 deep groove ball bearings. The bearing manufacturer is SKF, a company headquartered in Gothenburg, Sweden. The rotor materials are permanent magnets and silicon steel sheets. The electrical parameters of the motor are shown in Table 2.

The motor is driven by an IGBT inverter or a SiC inverter, with rated powers of 10 kW, respectively. The IGBT inverter is purchased from KEB, a company headquartered in Barntrup, Germany. The SiC inverter is developed in-house in the laboratory. The bearing voltage is measured using a conductive brush. The bearing current is measured through an intrusive measurement method, which requires modification of the motor end cover.

An insulating layer is inserted between the bearing outer race and the motor end cover. Additionally, an external connection is established between the bearing outer race and the motor housing by using a short wire beside the motor for measuring bearing current.

The SVPWM strategy, 400 V bus voltage, and 0.5 m of unshielded cable are used in the experiment. The SiC transistor and the IGBT transistor used in this paper are the C2M0080120D and IGW40N120H3, respectively. The rise and fall times of output voltages for SiC inverter and IGBT inverter are provided in Table 3.

Figure 7. The experimental platform for the bearing voltage and current tests.

Table 2. The electrical parameters of the motor.

Table 3. The rise and fall times of output voltage for inverters.

For deep groove ball bearings, when the rotational speed is below approximately 300 r/min, the lubricating grease cannot completely envelop the ball, resulting in metal-to-metal contact between the ball and the inner and outer races. The bearing oil film is short-circuited, preventing the establishment of bearing voltage.

When the bearing speed is relatively high, the lubricating grease can generally form a stable oil film, allowing for the establishment of bearing voltage. Therefore, in order to ensure the stable establishment of bearing voltage, the motor speed used in the experiment is set at 1200 r/min with a modulation ratio of M = 0.4 in this paper.

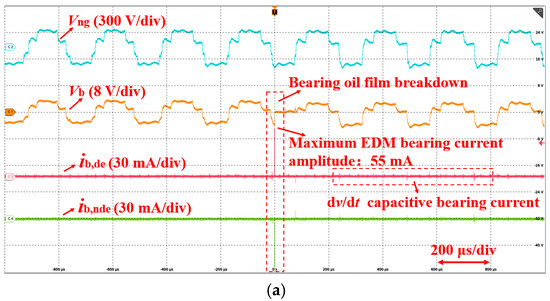

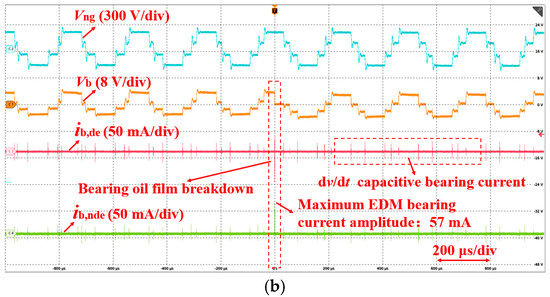

4.2. Experimental Results under IGBT and SiC Inverters Drive

The experimental results of the motor neutral point voltage Vng, bearing voltage Vb, and bearing current were obtained using IGBT and SiC inverters, as shown in Figure 8. ib,de and ib,nde are, respectively, driven-end and non-driven-end bearing currents of the motor, and Tb is the temperature of the bearing outer race. In Figure 8, under the IGBT and SiC inverters’ drive, the stable amplitudes of Vb are approximately Vb_IGBT ≈ Vb_SiC = 6.3 V.

It indicates that the stable amplitude of the Vb is significantly influenced by the switching frequency but is only slightly affected by the switching speed. In Figure 8a, the maximum value of ib,EDM__IGBT is 55 mA, while in Figure 8b, the maximum value of ib,EDM__SiC is 57 mA, with the amplitudes being nearly equal. Different high-bandwidth current probes were employed for repeated testing, revealing that the 2 mA current difference is not measurement error but a real difference.

An explanation of this phenomenon is as follows: when the bearing rotates steadily, the lubricating grease film is uneven, and the raceway roughness is difficult to predict. Consequently, when breakdown discharge occurs in the oil film, the breakdown impedance is also different, which leads to slightly different amplitudes of ib,EDM under the same test conditions.

In the test conditions shown in Figure 8, both IGBT and SiC inverters were used, and a total of 30 sets of ib,EDM were captured in each case. The results show that although the bearing voltage amplitudes are equal, all captured amplitudes of ib,EDM fluctuate around 55 mA, with variations not exceeding 4 mA. This current fluctuation is considered normal and is not a result of measurement error.

Figure 8. Measured waveforms of Vng, Vb, ib,de, and ib,nde (test conditions: SVPWM, Udc = 400 V, fs = 4 kHz, M = 0.4, Tb: 24~26 °C). (a) Under IGBT inverter drive; (b) under SiC inverter drive.

Since Vb_IGBT and Vb_SiC have similar amplitudes, the maximum amplitudes of ib,EDM__IGBT and ib,EDM__SiC are also approximately equal, indicating that the amplitude of Vb determines the energy of the ib,EDM.

Furthermore, from Figure 8, it can be observed that the capacitive bearing current ib,cap under the IGBT inverter is smaller than that in the SiC inverter, mainly due to the faster switching speed of the SiC inverter compared to the IGBT inverter.

According to Table 3, the switching speed of the SiC inverter is approximately one-tenth of that of the IGBT inverter. The amplitude of ib,cap is small, and the impact on bearing electric corrosion is also small. Under the IGBT inverter drive, ib,cap is generally neglected. However, under the SiC inverter drive, the impact of ib,cap on the bearing electric corrosion currently lacks relevant research conclusions.

4.3. Experimental Verification of Frequency Characteristics for Bearing Voltage and Current

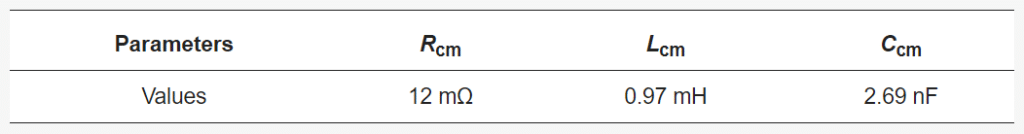

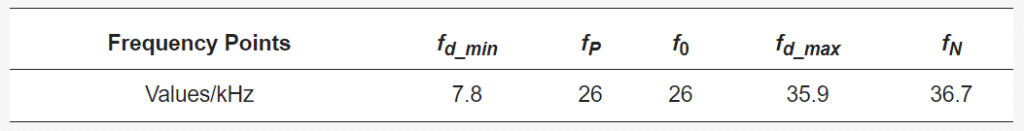

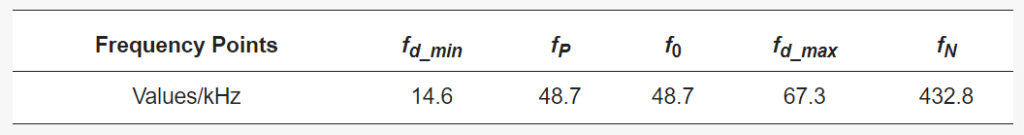

The experimental platform in Figure 7 is used for testing, and the measurement results of common-mode parameters of the motor and cable are obtained, as shown in Table 4. By substituting the parameters into Equations (7)–(11), the theoretical calculation results of points P, O, d_min, d_max, and N in Figure 6 are obtained. as shown in Table 5.

Table 4. The measured parameters of a common-mode equivalent circuit.

Table 5. Theoretical calculation results of frequency points for a Vb characteristic curve in the experimental system.

According to Table 5 and Figure 6, the analyses are as follows. When the switching frequency of the inverter used in the experiment exceeds 29.6 kHz, Vb begins to enter the danger zone in Figure 6. As the switching frequency increases, the amplitude of Vb increases significantly, reaching its maximum value at a frequency of 98.5 kHz. In the range from 98.5 kHz to 136.1 kHz, Vb begins to decrease, but it remains higher than the reference bearing voltage Vb*.

Therefore, when the switching frequency falls within the range from 29.6 kHz to 136.1 kHz, there is a significant risk of bearing electric corrosion. According to Figure 6, when the switching frequency exceeds 139.3 kHz, Vb starts to decrease below Vb*. In fact, constrained by electromagnetic interference and the control speed of the main controller, the switching frequency of the SiC inverter for the electric vehicle is generally lower than 100 kHz at present. Therefore, for the motor drive system adopted in the experiment, the Vb is located in zones ① and ② in Figure 6.

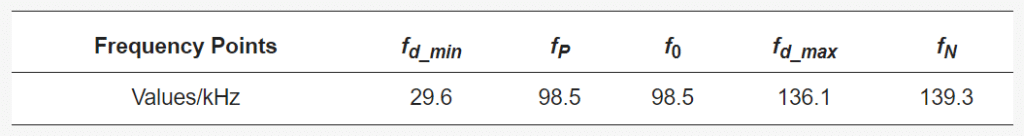

The theoretical calculation and experimental results of the Vb under different switching frequencies are obtained in Figure 9. The reference bearing voltage is Vb* = 6.3 V. When the switching frequency is less than 20 kHz, Vb increases slowly. In the range of 20 kHz–80 kHz, Vb increases quickly. Below 40 kHz, the theoretical calculations and experimental results are basically consistent. Above 40 kHz, with the increase in switching frequency, the error between the theoretical calculation and experimental results becomes more significant.

The analyses of error sources are as follows. Although the RLC lumped parameter equivalent circuit of the motor is simple, it is not accurate. In addition, there are measurement errors in the extraction of circuit parameters. Although there are errors at high frequencies, the overall variation trend of the bearing voltage is consistent with that of the frequency–characteristic curve depicted in Figure 6.

Figure 9. Variation trend of bearing voltage with switching frequency.

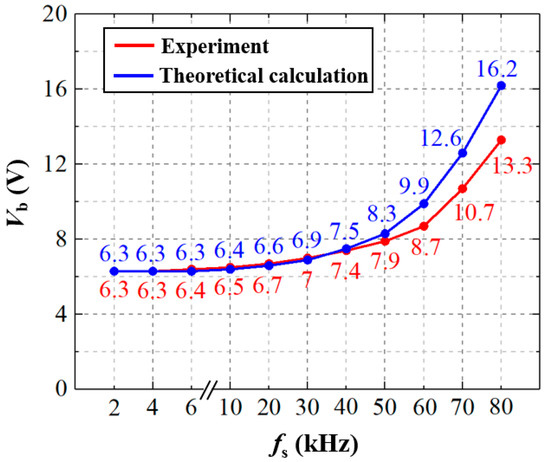

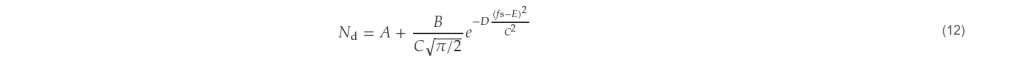

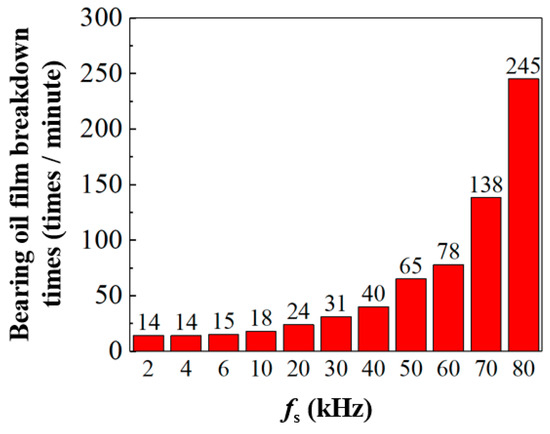

Figure 10 shows the number of ib,EDM occurrences (that is, the number of bearing oil film breakdown discharges) with the switching frequency per minute. The number of breakdown discharges was measured by taking the average value of multiple sample datasets. The results show that the increase in Vb could lead to the increased bearing breakdown discharges. The number of ib,EDM is approximately exponential with the rising switching frequency.

Based on Figure 10, the relationship between breakdown discharge times and switching frequency is obtained, as shown in Equation (12). Nd denotes the number of breakdown discharges. For the application in this paper, the values of the variables are A = 16.3, B = 8 × 107, C = 137.9, D = 2, and E = 349.

Figure 10. Variation trend of bearing oil film breakdown times with switching frequency.

The basic bearing voltage Vb*, especially at low switching frequency, already poses a significant threat to motor bearings. The increased switching frequency of the SiC inverter inevitably results in a further increase in bearing voltage. The dc bus voltage of the motor drive system is upgraded from 400 V to 800 V, which can double the bearing voltage. Therefore, with the increase in dc bus voltage and switching frequency, bearing voltage, and EDM bearing current are fatal to bearing damage, and effective suppression measures must be taken.

5. Design of Common-Mode Filter for Reducing Bearing Voltage and Current

The high switching frequency of the SiC inverter is advantageous for reducing the volume of the filter. Employing a common-mode filter to improve the frequency characteristics of a common-mode equivalent circuit and to suppress bearing voltage is an effective approach to mitigate bearing electric corrosion.

5.1. Theoretical Calculation and Experimental Verification for Common-Mode Filter

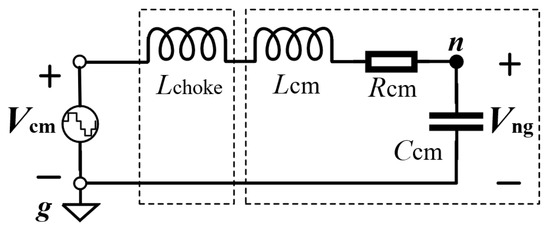

The actual operating frequency of the SiC inverter used in the experiment is 50 kHz. According to Table 5, the Vb of the experimental motor is located in zone ② in Figure 6, which is the danger zone. In order to greatly reduce the Vb, it is necessary to design a common-mode filter to ensure that Vb is located in zone ④, so as to reduce the risk of bearing electric corrosion. The common-mode equivalent circuit of the motor drive system with a common-mode filter is shown in Figure 11.

Figure 11. Common-mode equivalent circuit of the motor drive system with a common-mode filter.

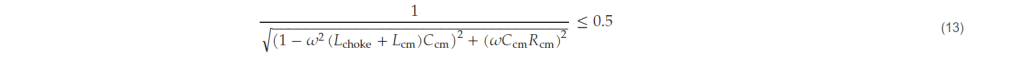

In order to attenuate the Vb by at least half of the reference bearing voltage Vb*, according to Equation (6), the Equation (13) can be obtained:

Substituting the parameters in Table 4 into Equation (13), Lchoke ≥ 10.33 mH is obtained. The inductance of common-mode filter needs to be greater than 11 mH. In order to achieve Vb ≤ 0.5Vb*, the actual designed common-mode filter has a certain margin, and the final inductance value is 13 mH.

There is an error in the actual and theoretical design of the inductance value, which mainly arises from the following three aspects: the presence of other harmonic components in the common-mode excitation Vcm, inherent errors in the lumped parameter equivalent circuit, measurement errors in the extraction of common-mode parameters, and parasitic parameters in the filter. The above factors cause the error between the theoretical and actual inductance values in this paper.

According to the equivalent circuit model shown in Figure 11, when the inductance of the common-mode filter changes, the frequency characteristics of the motor drive system also change accordingly. Correspondingly, the curve of Vb also changes with frequency in Figure 6. According to Equations (7)–(11), the theoretical calculation results of each frequency point at the curve in Figure 6 are shown in Table 6 by using a 13 mH common-mode filter.

Table 6. Theoretical calculation results of frequency points for the Vb characteristic curve in the experimental system (Lchoke = 13 mH).

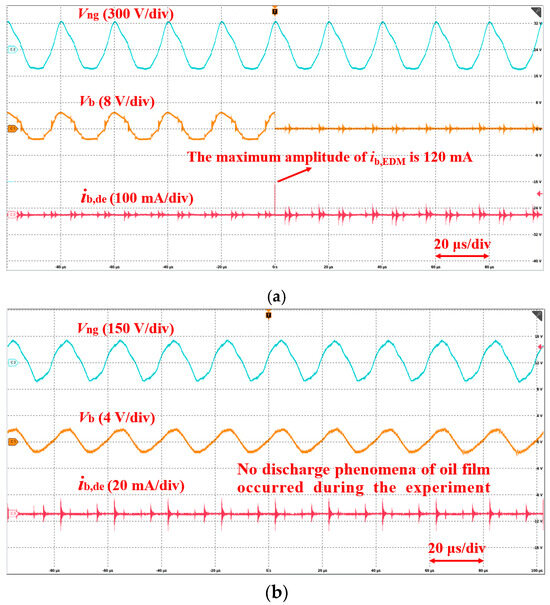

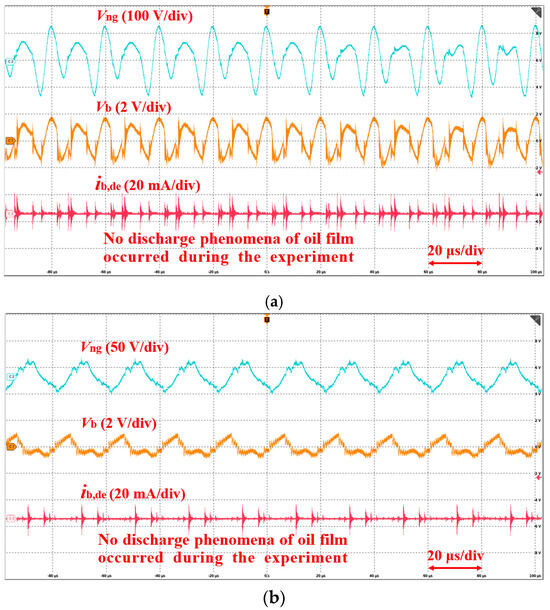

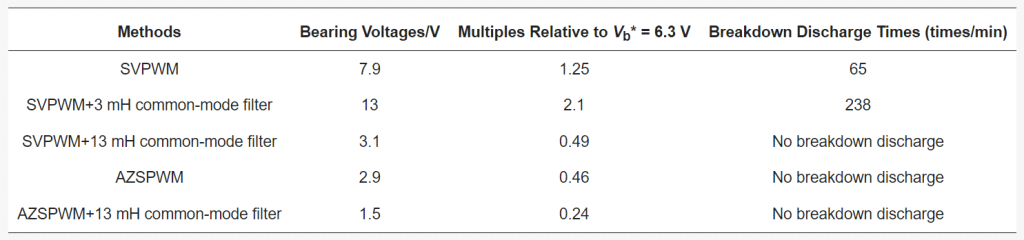

The experimental waveforms are shown in Figure 12. In Figure 12a, the amplitude of Vb is 7.9 V without a common-mode filter, and the maximum amplitude of ib,EDM is 120 mA. Vb is located in zone ② of Figure 6. In Figure 12b, after using a common-mode filter, the measured amplitude of Vb is 3.1 V, and Vb is located in zone ④ of Figure 6, which is reduced to 0.49 times of the reference value Vb* = 6.3 V. By using a common-mode filter, significant attenuation of Vb is obtained, and no discharge of oil film occurs during the experiment.

Figure 12. Measured waveforms of Vng, Vb, and ib (test conditions: SVPWM, Udc = 400 V, fs = 50 kHz, M = 0.4, Tb: 24~26 °C). (a) Without common-mode filter; (b) with a 13 mH common-mode filter.

5.2. Negative Effects Caused by Improper Design of a Common-Mode Filter

In order to suppress electromagnetic interference in practical applications, a magnetic ring is often used at the output end of inverter, as shown in the red box in Figure 1. The magnetic ring can be equivalent to a common-mode filter with a single turn coil, which has a small inductance. The Vb is usually located in zone ① of Figure 6 when using an IGBT inverter with a low switching frequency. According to Figure 6 and Equation (6), the amplitude of Vb is basically not increased when the common-mode magnetic ring is installed at the output end of inverter.

Therefore, the magnetic ring is used to suppress electromagnetic interference while minimizing the negative impact on Vb. However, when using a SiC inverter with a high switching frequency, Vb is located in zone ② in Figure 6. If the magnetic ring is still installed at the output end of the inverter to suppress electromagnetic interference, according to Equation (6), Vb would increase significantly, thereby increasing the risk of bearing electric corrosion.

To illustrate the above issue, a common-mode filter with a small inductance of 3 mH is used for the analysis. The frequency points of the curve in Figure 6 are recalculated and the results are shown in Table 7. According to Figure 6 and Table 7, if the inverter still adopts the switching frequency fs = 50 kHz, which is close to the resonant frequency of the system in Table 7, the amplitude of Vb is large. As a result, the bearings will face a significant risk of electric corrosion.

Table 7. Theoretical calculation results of frequency points for the Vb characteristic curve in the experimental system (Lchoke = 3 mH).

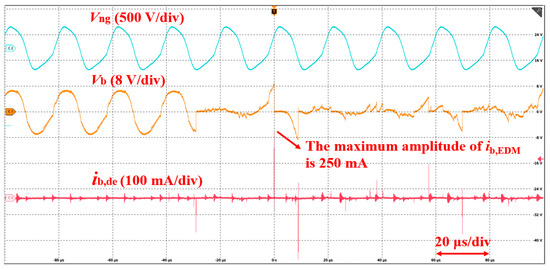

Still using the same testing conditions as in Figure 12, the experimental results are shown in Figure 13. The measured amplitude of Vb reaches 13 V, which is 65% higher than that (7.9 V) in Figure 12a. This significantly increases the breakdown times and discharge energy of the bearing oil film. The number of breakdown discharges per minute measured is as high as 238 times, and the maximum EDM bearing current is 250 mA, which is approximately twice that (120 mA) shown in Figure 12a.

Based on the theoretical and experimental results above, the switching frequency fs = 50 kHz in the experiment is close to the peak point frequency in Figure 6, inevitably leading to excessive bearing voltage and serious bearing corrosion.

Figure 13. Measured waveforms of Vng, Vb, and ib (test conditions: SVPWM, Udc = 400 V, fs = 50 kHz, M = 0.4, Tb: 24~26 °C, Lchoke = 3 mH).

In summary, for the SiC motor drive system, the design of a common-mode filter or magnetic ring needs to consider the suppression effects on both electromagnetic interference and bearing voltage. It is essential to refer to the design methods proposed in Section 3. Otherwise, improper filter design may exacerbate the bearing electric corrosion.

6. The Suppression Method for Bearing Current in a Motor Drive System with a High-Voltage SiC Inverter

In order to relieve the design pressure of the bearing in the motor drive system with a high voltage and high frequency, the AZSPWM strategy is adopted to weaken the common-mode voltage of the inverter from the source. Then, a common-mode filter is adopted for the output end of the inverter to further reduce the bearing voltage, reducing the discharge times and the discharge energy of the bearing oil film.

6.1. The AZSPWM Strategy

With the SVPWM strategy, the maximum value of the common-mode voltage is Udc/2 when using the zero vector. A non-zero vector modulation strategy can be used to reduce the common-mode voltage amplitude by canceling the zero vector.

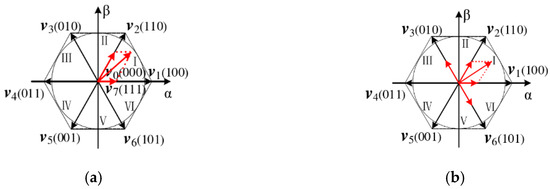

Considering the switching loss, modulation ratio, and harmonics, the AZSPWM strategy is adopted in this paper. The comparison of the vector synthesis for SVPWM and AZSPWM-1 in sector I is shown in Figure 14. The idea of AZSPWM-1 is to replace the zero vector by using two non-zero vectors in opposite directions acting at the same time, so that the amplitude of the common-mode voltage is suppressed to Udc/6.

Figure 14. Comparison of vector syntheses for different modulation strategies (taking sector I as an example). (a) SVPWM; (b) AZSPWM-1.

The AZSPWM strategy is divided into three types: AZSPWM-1, AZSPWM-2, and AZSPWM-3. The suppression effect on the common-mode voltage is the same for all three modulation strategies. For AZSPWM-2 and AZSPWM-3, the two bridge arms of the inverter need to operate simultaneously, leading to increased losses. Therefore, the AZSPWM-1 strategy is adopted. The AZSPWM-1 strategy may increase current harmonics, but the high switching frequency of the SiC inverter can reduce these current harmonics, compensating for this drawback.

With the AZSPWM-1 strategy, the common-mode voltage waveform is shown in Figure 15. The amplitudes are different in the even sector and odd sector, but the maximum value is Udc/6, which is one-third of the maximum value Udc/2 under the SVPWM strategy.

Figure 15. Diagram of common-mode voltage waveform under AZSPWM-1 strategy. (a) Even sector; (b) odd sector.

6.2. The Suppression Effect of Bearing Voltage and Bearing Current

Still using the same testing conditions as Figure 12, the experimental results are shown in Figure 16. In Figure 16a, the AZSPWM-1 strategy is adopted and the amplitude of Vb is reduced to 2.9 V, which is 63% lower than that of 7.9 V driven by SVPWM in Figure 12a. In Figure 16b, the combination of AZSPWM-1 and the 13 mH common-mode filter is adopted. The amplitude of Vb is reduced to 1.5 V and the Vb is greatly attenuated. During the experiment, no discharge phenomena occurred.

Figure 16. Measured waveforms of Vng, Vb, and ib (test conditions: SiC inverter, AZSPWM-1, Udc = 400 V, fs = 50 kHz, M = 0.4, Tb: 24~26 °C). (a) Without common-mode filter; (b) with a 13 mH common-mode filter.

The comparison results of bearing voltage amplitudes and breakdown discharge times are shown in Table 8 under different suppression methods. The combination of AZSPWM-1 and the common-mode filter achieves the best suppression effect, reducing the bearing voltage to 1.5 V. It effectively suppresses the EDM bearing current and is highly suitable for a motor drive system with a high voltage and high frequency.

Table 8. Comparison results of bearing voltage and discharge times under different suppression methods.

7. Conclusions

This paper investigates the characteristics and suppression methods of bearing voltage and EDM bearing current under SiC inverter drive. By establishing the common-mode equivalent circuit of the motor drive system, the frequency characteristics of bearing voltage are revealed. The suppression method is proposed, which is suitable for a motor drive system with a high voltage and high frequency. Through theoretical analysis and experimental validation, the following conclusions are drawn.

Compared to a traditional IGBT inverter, the SiC inverter with a high switching frequency increases the amplitude of bearing voltage, exacerbating the risk of bearing electric corrosion. The selection of switching frequency must consider the impact on the bearing voltage and the EDM bearing current.

For motor drive systems with a SiC inverter, the design of the common-mode filter or magnetic ring needs to consider the influence on bearing voltage and current. Otherwise, negative effects may occur, aggravating bearing electric corrosion. The proposed design method of common-mode filter can improve the frequency characteristics of bearing voltage, attenuating the bearing voltage to half of the reference bearing voltage and keeping it in the safe operating zone.

The AZSPWM-1 strategy can attenuate the bearing voltage to around half of the reference bearing voltage. When combining AZSPWM-1 and a common-mode filter, the bearing voltage is reduced to around one-fourth of the reference bearing voltage, achieving the best suppression effect. This method effectively reduces the breakdown times of lubricating grease oil film, which is suitable for motor drives with a high voltage and high frequency in electric vehicles.

Authors

Mingliang Yang, Yuan Cheng, Bochao Du, Yukuan Li, Sibo Wang, Shumei Cui.

Original – MDPI

-

LATEST NEWS2 Min Read

Navitas Semiconductor announced its participation in the upcoming Power Electronics International conference on April 16th– 17th 2024, in Brussels, Belgium.

Grid reliability is a key factor in a $1.3 trillion power semiconductor opportunity as Navitas’ technologies accelerate the transition from fossil fuels to renewable energies. Navitas will introduce the latest GaNFast™ and GeneSiC™ products to the European audience, including new Gen-3 Fast SiC for high-power and higher-speed performance, plus GaNSafe™ – the world’s most protected GaN power devices.

Navitas will present the following on April 17th:

- “3.3 kV SiC MOSFETs Accelerate Grid-Connected Energy Storage,” Dr. Ranbir Singh, EVP GeneSiC

Synopsis: The grid supplies energy from generators and delivers it to customers via transmission and distribution (T&D) networks. In the U.S., the use of electricity storage to support and optimize T&D has been limited due to high storage costs and limited design and operational experience. Recent improvements in storage and power technologies, however, coupled with changes in the marketplace, herald an era of expanding opportunity for electricity storage. SiC inverters will revolutionize electricity delivery, renewable energy integration, and energy storage. It is well-recognized that silicon-based semiconductors have inherent limitations that reduce their suitability for utility-scale applications.

- “Bi-directional circuits open up new opportunities in off-grid applications,” Alfred Hesener, Senior Director Industrial and Consumer Applications

Synopsis: Bi-directional circuits are critical to effectively smooth the supply/demand variation in renewable energy applications. In the past, they were expensive to make and complex to implement in power electronics applications. Wide bandgap GaN power ICs with integrated drive and advanced circuit functions deliver easy-to-use, reliable, high power density, and functionality for power factor correction circuits, solar inverters, and solid-state circuit breakers.

Original – Navitas Semiconductor

-

EPC Space announced a distribution agreement with Avnet, a global distributor of electronic components and services. Avnet will be a global distributor for EPC Space’s line of radiation hardened (Rad Hard) GaN power devices qualified for satellite and high-reliability applications.

EPC Space offers a family of Rad Hard power GaN devices that includes discrete transistors, Integrated Circuits (ICs), and Modules that offer significant performance advantages over competitive silicon-based space level power devices. EPC Space’s GaN technology devices are smaller, have lower resistance, and have superior switching performance compared to silicon-based components and solutions.

Critical spaceborne applications that benefit from the performance improvements that EPC Space devices offer include satellite’s DC-DC converters, reaction and momentum wheels, solar array drive assembly, micro-pumps for propulsion systems, and more.

“Partnering with Avnet, a global leader in distribution solutions, allows EPC Space to offer timely and reliable service to customers seeking high reliability GaN power solutions,” said Bel Lazar, EPC Space’s CEO.

Original – EPC Space

-

INDUSTRY PAPERS16 Min Read

Abstract

In this paper, a novel asymmetric trench SiC MOSFET with a Poly-Si/SiC heterojunction diode (HJD-ATMOS) is designed to improve its reverse conduction characteristics and switching performance. This structure features an integrated heterojunction diode, which improves body diode characteristics without affecting device static characteristics.

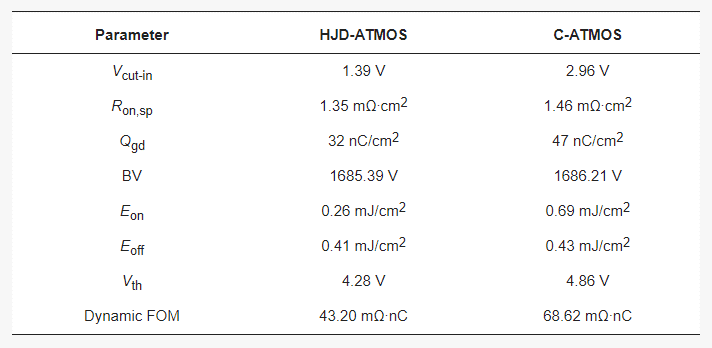

The heterojunction diode acts as a freewheeling diode during reverse conduction, reducing the cut-in voltage (Vcut-in) to a lower level than conventional asymmetric trench SiC MOSFET (C-ATMOS), while maintaining a similar breakdown voltage. Meanwhile, the split gate structure reduces gate-to-drain charge (Qgd). Through TCAD simulation, the HJD-ATMOS decreases Vcut-in by 53.04% compared to the C-ATMOS. Both Qgd and switching loss are reduced, with a decrease of 31.91% in Qgd and 40.29% in switching loss.

1. Introduction

The wide bandgap semiconductor properties of silicon carbide (SiC) make it a promising candidate for the development of future power switching devices. This is primarily due to SiC possessing properties such as a strong breakdown field, high physical and chemical stability, high thermal conductivity, and high electron saturation velocity.

SiC devices can operate in harsh environments due to their wide band gap of 3.25 eV and high thermal conductivity of 5 W/(cm·K). The SiC MOSFET is the most significant SiC power switching device due to its lack of trail current. This reduces switching loss and radiator volume, improving system power density.

SiC MOSFETs commonly make use of parasitic body-PN diodes as freewheeling diodes (FWD) in power inverter and converter systems. However, parasitic body-PN diodes in SiC MOSFETs are not ideal for use as freewheeling diodes. The reasons for this are as follows: Stacking faults (SFs) in SiC devices may cause reliability issues and increase conduction loss.

Although recent papers concerning the measured degradation of SiC MOSFETs show a high level of current threshold (about 5× the nominal current or more than 1000 A/cm2) for the starting of bipolar degradation, bipolar degradation effects can still occur in SiC MOSFETs under large cyclic pulse current densities. This will limit the application of SiC MOSFET devices in key areas, such as the surge current that flows through a diode during the start-up of a power converter, which can be more than ten times its rated current.

Furthermore, the body diode’s Vcut-in voltage (~2.7 V) is much higher than that of its silicon counterparts due to SiC’s wide bandgap. To overcome the drawbacks of parasitic body-PN diodes, numerous approaches have been devised to deactivate them. One approach is to integrate SiC MOSFETs with Schottky barrier diodes (SBDs). However, the use of external diodes not only introduces parasitic inductance, limiting switching frequency, but also consumes additional area in the package. And Schottky contacts suffer from a significant increase in reverse leakage current at high temperatures.

Furthermore, SiC MOSFETs with low-barrier and heterojunction diodes are available. Heterojunction diodes formed between polysilicon and SiC are attractive. Shenoy and Baliga, and Yamagami et al. presented studies on heterojunction diodes using P-Poly-Si and n-6H-SiC, and Poly-Si and 4H-SiC, respectively.

Both studies demonstrated low-forward-voltage Schottky-like characteristics. Ni et al. proposed a trench SiC MOSFET integrating polysilicon/SiC HJD, exhibiting excellent freewheeling diode (FWD) performance in both the first and third quadrants. The HJD’s unipolar behavior, similar to that of a Schottky diode, effectively suppresses the turn-on of the problematic body diode, mitigating the aging degradation observed in conventional SiC MOSFETs.

Additionally, HJDs reduce reverse recovery voltage and losses, enhancing long-term operational reliability. Furthermore, HJD integration eliminates the need for a separate SBD, leading to a smaller chip area, simpler packaging, and reduced overall system cost. This also minimizes parasitic inductance arising from additional components.

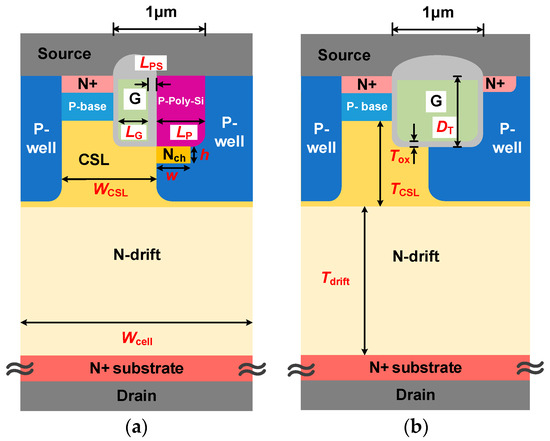

A novel asymmetric trench SiC MOSFET with a heterojunction diode at the right of the gate trench is proposed and simulated in this paper. The structure includes a trench gate with split-gate electrodes and a thicker P-Poly-Si layer, resulting in reduced gate charge and improved switching performance. To suppress the depletion layer, an n-type doped current spreading layer (N-CSL) is formed under the entire P-well region.

To maintain the breakdown voltage (BV) of the device structure while maintaining transfer and output characteristics similar to those of C-ATMOS, the depth of the P-well on the right side is not changed. The N-channel (Nch) is positioned below the P-Poly-Si and in contact with the CSL. The integrated HJD structure of the proposed device eliminates the requirement for an anti-parallel SiC SBD during reverse conduction. The HJD turns on at a low source–drain voltage (Vsd), thus eliminating bipolar degradation by inactivating the body diode. The split gate results in a decrease in gate charge, leading to a reduction in switching losses in the HJD-ATMOS without affecting other characteristics.

2. Device Structure and Mechanism

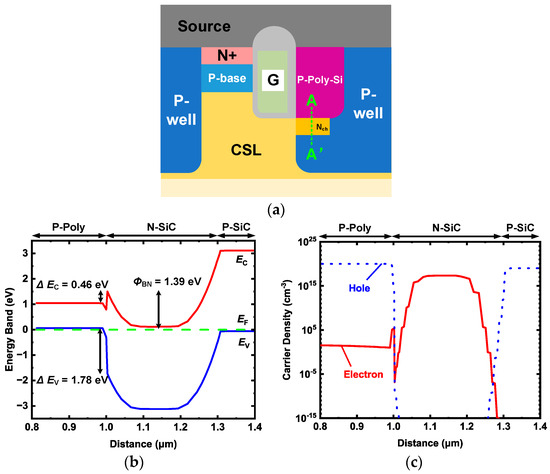

The schematic cross section of HJD-ATMOS and C-ATMOS is shown in Figure 1. Similar to C-ATMOS, the device forms an inversion layer channel in the first quadrant to facilitate electron conduction. The N-CSL layer on the N-drift region reduces the on-resistance. Deep P-wells are used to reduce the electric field stress in the gate oxide at the trench bottom and corner.

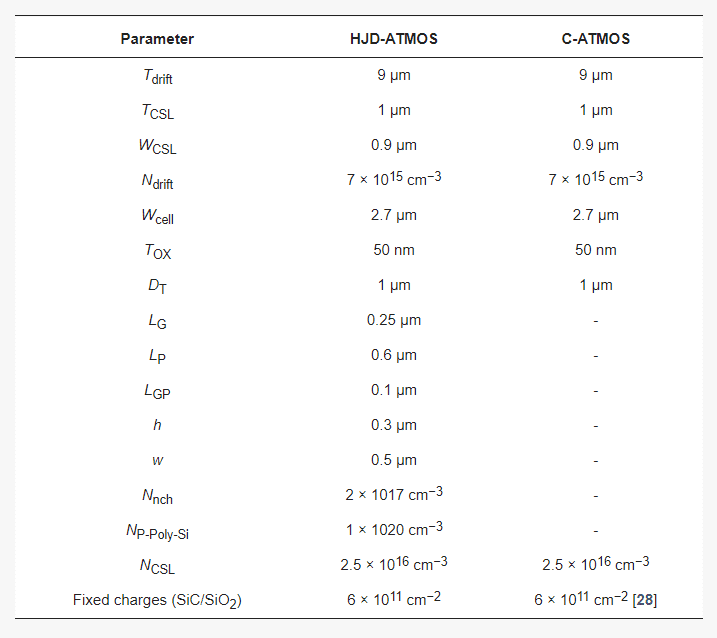

The primary distinction is the body diode structure. The Nch region under the P-Poly-Si provides a low-barrier path for electrons. Meanwhile, the HJD-ATMOS has a split gate and HJD structure on the right of the gate oxide layer. The split gate structure uses only a portion of the trench space for the gate electrode, while the other part is thicker P-Poly-Si that forms a portion of the HJD structure. The HJD-TMOS facilitates low-voltage conduction by allowing electrons to cross the lower heterojunction barrier in the third quadrant. The structure of Nch and N-channel doping concentration (Nnch) will be further discussed based on this optimization in this paper. Device specifications are presented in Table 1.

Figure 1. Schematic cross section of (a) HJD-ATMOS and (b) C-ATMOS.

Table 1. Main parameters used in the simulation.

Sentaurus TCAD simulations are used to analyze the performances of the HJD-ATMOS and the C-ATMOS, considering doping and temperature-dependent Shockley–Read–Hall and Auger recombination, doping-dependent transport, impact ionization, band narrowing, high-field velocity saturation, and mobility degradation, as well as fixed charges at the SiC/SiO2 interface for closer simulation results to experimental data.

The energy band diagram of the P-Poly-Si/N-SiC heterojunction at thermal equilibrium is shown in Figure 2b. The energy band diagram at thermal equilibrium along the A-A’ cut-line is shown in Figure 2a. The heterojunction has a conduction energy gap of 0.46 eV and a valence barrier energy gap of 1.78 eV. The electron barrier height ΦBN is determined by the Fermi level energy Ef and the conduction band peak energy Ec, which is about 1.39 eV.

Figure 2c shows the simulated carrier density at the heterojunction interface under forward bias at the rated voltage. Electrons are injected from N-SiC to P-poly, but there are few holes from P-poly to N-SiC due to the high hole barrier. Therefore, the HJD exhibits unipolar action, similar to the SBD.

Figure 2. (a) Schematic cross section of HJD-ATMOS; (b) energy band diagram at thermal equilibrium along the A-A’ cut-line; (c) carrier density of the HJD when forward biased at rated voltage.

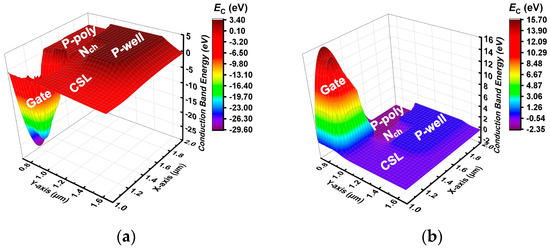

We also constructed a 3D band diagram of the device to better observe the working state of the device. Figure 3a shows the 3-D conduction band energy distribution of the device at Vds = 10 V and Vgs = 15 V. The band energy of Nch is higher than that of N-CSL, which prevents electron current from flowing to P-poly and enables the device to work normally like C-ATMOS.

Figure 3b shows the distribution of the devices when Vds = −5 V and Vgs = −5 V. The band energy of Nch is lower than that of N-CSL, resulting in electron current flowing from N-CSL to P-poly and preventing the turn-on of parasitic body-PN diodes.

Figure 3. Three-dimensional conduction band energy distribution between P-poly, gate, Nch, N-CSL, and P-well (a) when conduction is forward and (b) when conduction is reverse.

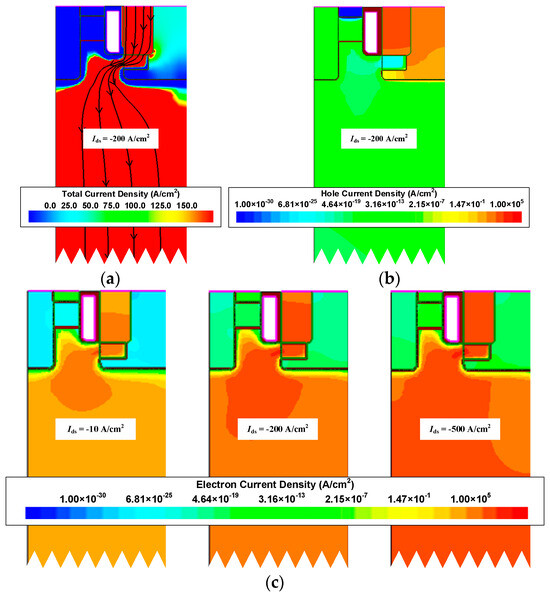

Figure 4 shows the distribution of the total current density, hole current density, and electron current density of the device. From the total current density distribution, it can be seen that the current does not flow from P-Poly-Si to P-well. But a high current density is also noted at the gate corner of P-Poly-Si, which should be noted in use. From the hole current density distribution, it can be seen that holes do not enter N-drift.

This is due to the difference in the band gap between SiC and polysilicon. Since the energy barrier height between the SiC and polysilicon junctions in the valence band is very large, in the HJD-ATMOS, electron current can move toward the source while hole current cannot move toward the drain. The device can operate normally at electron current densities of 10 A/cm2 and 500 A/cm2.

Figure 4. (a) Total current density distribution, (b) hole current density distribution, and (c) electron current density distribution at low and high current in the reverse conduction.

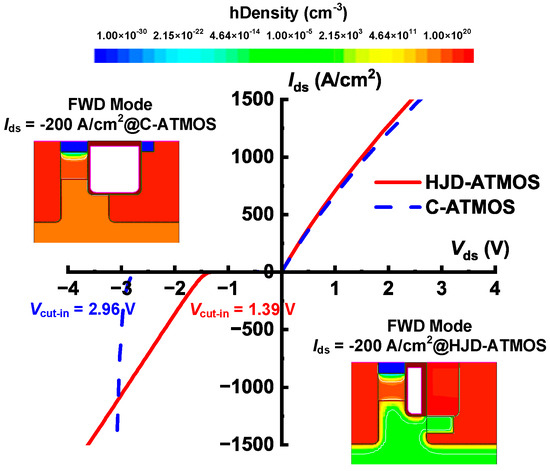

Figure 5 shows the I–V curves of HJD-ATMOS and C-ATMOS in forward and reverse conduction at room temperature. The steeper slope of the I–V curve of HJD-ATMOS in the first quadrant indicates that its specific on-resistance (Ron,sp) is lower than that of C-ATMOS. This is because the presence of Nch in HJD-ATMOS results in a smaller depletion region of P-well on N-CSL, leading to a wider current conduction region.

According to the calculations, at Vgs = 15 V and Ids = 200 A/cm2, the Ron,sp values for HJD-ATMOS and C-ATMOS are 1.35 mΩ∙cm2 and 1.46 mΩ∙cm2, respectively. In the third quadrant, at Ids= −10 A/cm2, HJD-TMOS exhibits a significantly lower Vcut-in of only 1.39 V compared to the PN diode of C-TMOS. As a result, HJD-ATMOS is capable of reducing switching losses.

The rated operating current of the device in the third quadrant is generally Ids = −200 A/cm2. This means that the proposed HJD-ATMOS has a clear advantage over C-ATMOS in that it can start working at a lower voltage. The hole density distribution diagram in Figure 5 for Ids = −200 A/cm2 shows that the integrated HJD effectively suppresses minority carrier injection, reducing bipolar degradation.

Figure 5. First and third quadrant characteristics of HJD-ATMOS and C-ATMOS.

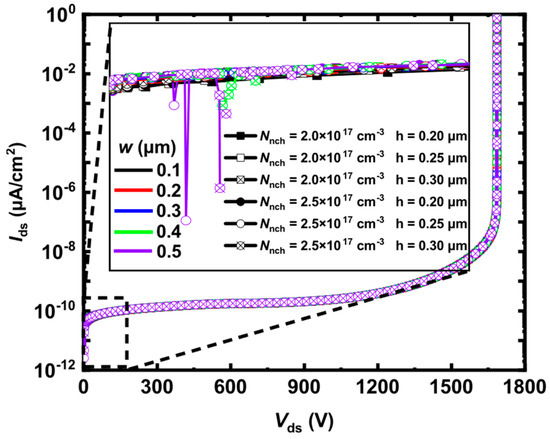

In Figure 6, the local magnification shows that the HJD-ATMOS is affected by current spikes due to leakage. The figure demonstrates the change in breakdown voltage as a function of h and w when Nnch is, respectively, 2 × 1017 cm−3 and 2.5 × 1017 cm−3. It can be observed that when Nnch is 2.5 × 1017 cm−3, with h at 0.25 μm and w at 0.5 μm, the spike in the current is large, indicating the occurrence of leakage. When Nnch is 2.5 × 1017 cm−3, increasing h to 0.30 μm and w to 0.4 μm also results in leakage.

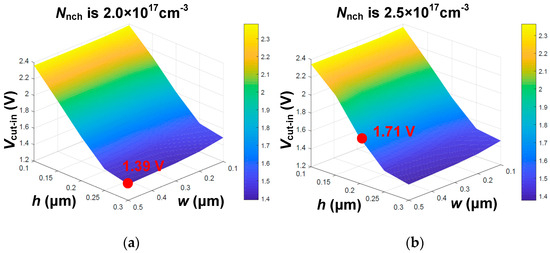

However, when Nnch is 2.0 × 1017 cm−3 and h increases to 0.3 μm, the device does not exhibit leakage, demonstrating that variations in Nnch have a significant impact on device performance. As shown in Figure 7, Vcut-in varies significantly with h. The minimum point of Vcut-in is 1.31 V at Nnch = 2 × 1017 cm−3, which is lower compared to its value of 1.71 V at Nnch = 2.5 × 1017 cm−3 and h = 0.2 μm.

This point represents the critical condition for the device not exhibiting leakage when Nnch = 2.5 × 1017 cm−3. After h is greater than 0.25 μm, the variation in Vcut-in with h tends to be flat, and if the value of h is larger, the protective effect of P-well on the gate oxide will also be weakened, and it will also increase the difficulty of process manufacturing.

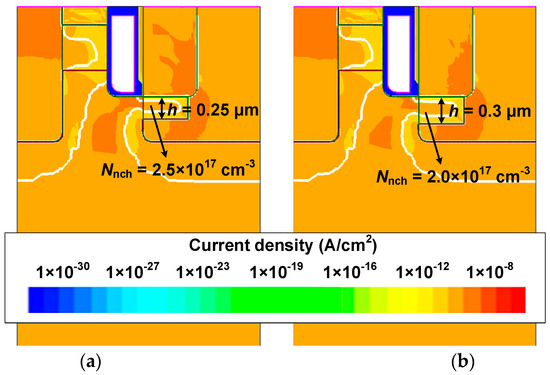

As can be seen from Figure 8, when the device Vds is 0 V, Nnch is 2.5 × 1017 cm−3, and h is 0.25 μm, the HJD-ATMOS has more leakage than the device with Nnch is 2.0 × 1017 cm−3 and h is 0.30 μm. The darker regions in the current density plot for the HJD-ATMOS with Nnch at 2.5 × 1017 cm−3 and h at 0.25 μm are larger than those with Nnch at 2.0 × 1017 cm−3 and h at 0.30 μm, indicating higher leakage currents. This also confirms the hypothesis that the breakdown voltage spike is caused by heterojunction leakage. So the results indicate that Nnch = 2 × 1017 cm−3, h = 0.3 μm, and w = 0.5 μm are the optimal values.

Figure 6. The breakdown voltage varies with h, w, and Nnch, when Nnch is 2.0 × 1017 cm−3 and 2.5 × 1017 cm−3, h is 0.20 μm, 0.25 μm and 0.30 μm, and w is 0.1 μm to 0.5 μm, respectively.

Figure 7. Vcut-in varies with h, w, and Nnch, when Nnch is (a) 2.0 × 1017 cm−3, and (b) 2.5 × 1017 cm−3.

Figure 8. Current density distribution when (a) Nnch is 2.5 × 1017 cm−3, h is 0.25 μm, and (b) Nnch is 2.0 × 1017 cm−3, h is 0.30 μm at Vds = 0 V.

3. Simulation Results and Discussion

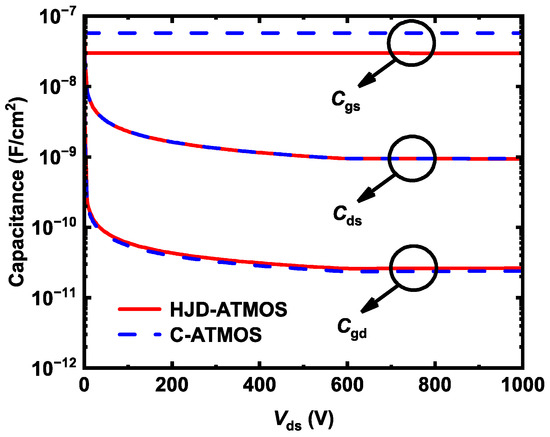

Figure 9 shows the capacitances of HJD-ATMOS and C-ATMOS. Gate voltage was fixed at 0 V, a 1 MHz AC signal was applied, and drain voltage was swept from 0 to 1000 V. HJD-ATMOS has lower gate-to-source capacitance (Cgs) than C-ATMOS due to the smaller contact area with the source caused by the split gate structure. HJD-ATMOS’s gate-to-drain capacitance (Cgd) does not decrease.

This is because the P-well blocks the right side of the gate of C-ATMOS, performing a similar function as the split gate. Therefore, it can be observed that the Ciss (Cgs + Cgd) of the HJD-ATMOS with split gates is also smaller than that of the C-ATMOS.

Figure 9. The device capacitance of HJD-ATMOS and C-ATMOS.

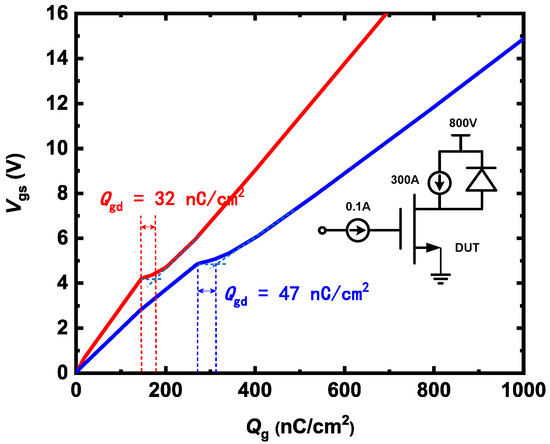

Gate-to-drain charge (Qgd) is critical for power device switching speed in device applications. Figure 10 shows a test circuit to simulate HJD-ATMOS and C-ATMOS gate charges during turn-on. The miller plateau height of HJD-ATMOS is less than that of C-ATMOS, indicating that the threshold voltage of HJD-ATMOS is smaller than that of C-ATMOS.

Because the gate charge is proportional to the gate capacitance, the HJD-ATMOS has a lower gate charge (Qg) and Qgd compared with the C-ATMOS. The Miller platform in HJD-ATMOS is shorter because of the reduced gate area. The Qgd values for HJD-ATMOS and C-ATMOS are 32 nC/cm2 and 47 nC/cm2, respectively. Qgd of HJD-ATMOS decreased by 31.91% compared to C-ATMOS. Reduced Qgd leads to a smaller high-frequency figure of merit in HJD-ATMOS.

Figure 10. The gate charge characteristics of HJD-ATMOS and C-ATMOS.

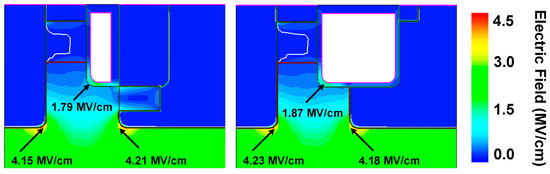

Figure 11 shows the electric field distribution at the breakdown of HJD-ATMOS and C-ATMOS. The electric field at the gate oxide of HJD-ATMOS is smaller than that of C-ATMOS. This is because the presence of the Nch introduces a portion of the electric field into this region, which alleviates the electric field that the gate oxide withstands.

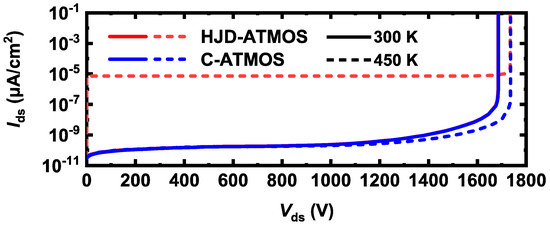

Although increasing the electric field at the heterojunction raises leakage current risk, it is a trade-off for improved reverse conduction performance. Figure 12 shows the blocking characteristics of the HJD-ATMOS and the C-ATMOS at room temperature and high temperature. At room temperature, the data are represented by solid lines, whereas at elevated temperatures, they are depicted by dashed lines. HJD-ATMOS and C-ATMOS have similar breakdown voltages at room temperature. But the leakage current of the HJD-ATMOS increases at high temperature due to the increased thermal energy of the charge carriers.

The generation of leakage currents, as demonstrated and discussed in Figure 6 and Figure 8, arises due to leakage occurring at the heterojunction, where higher Nnch and greater values of thickness h both contribute to this effect. By improving the semiconductor material growth process, reducing defects and traps, and enhancing the material quality and interface integrity, it is possible to mitigate non-ideal scattering and trap effects experienced by charge carriers at the heterojunction interface, thus suppressing the leakage current.

While the HJD-ATMOS structure does indeed experience leakage under temperature influence, this leakage is within acceptable limits, with the level of leakage current being 1 × 10−5 μA/cm2.

Figure 11. Electric field distribution for the HJD-ATMOS and the C-ATMOS at BV.

Figure 12. Blocking characteristics of the HJD-ATMOS and the C-ATMOS.

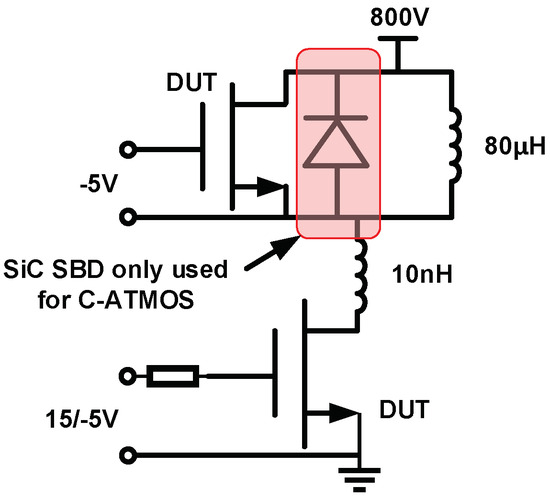

Figure 13 shows a double pulse test circuit for investigating switching characteristics. This is a common circuit configuration employed in device testing. Stray inductance is 10 nH, and load inductance is 80 μH. The gate voltage source (Vg) is turned on from −5 V to 15 V at t = 16 µs and turned off from 15 V to 0 V at t = 11 µs.

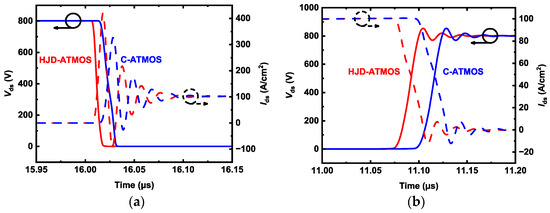

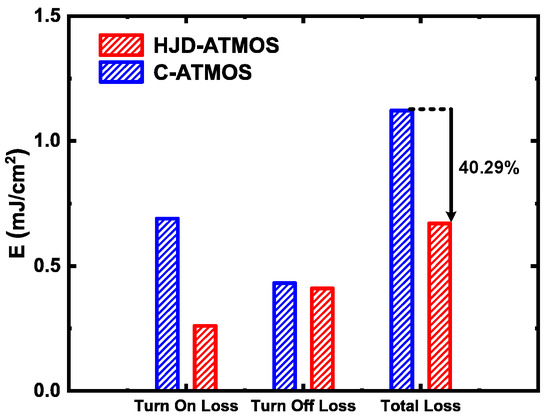

Figure 14 shows the switching waveforms of devices. The switching speed of the HJD-ATMOS is faster than that of the C-ATMOS with an external SBD diode, which results in a smaller switching loss. Figure 15 compares the switching losses between the two devices. In HJD-ATMOS, the turn-on loss (Eon) is 0.26 mJ/cm2, and the turn-off loss (Eoff) is 0.41 mJ/cm2, which demonstrate a reduction of 62.32% and 4.65%, respectively, compared to C-ATMOS.

The total switch loss of HJD-ATMOS is reduced by 40.29% compared to C-ATMOS. This is due to the smaller Qgd compared with the C-ATMOS. Reduced switching losses in power electronic devices are instrumental in improving operational longevity and reliability. As losses during switching are directly proportional to heat generation, a significant decrease in these losses curtails thermal build-up, mitigating the risk of device overheating and extending its operational life.

This reduction also sustains lower junction temperatures, crucial for preventing material degradation in high-power-density applications where maintaining low operating temperatures is vital for ensuring long-term stability and reliability. Furthermore, minimizing switching losses allows power converters and similar equipment to function efficiently at elevated frequencies without sacrificing efficiency, empowering designers to develop compact, lightweight systems while consistently meeting reliability standards.

Figure 13. A circuit for simulating switching with a double pulsed test.

Figure 14. The switching characteristics of HJD-ATMOS and C-ATMOS, including the (a) turn-on process and (b) turn-off process.

Figure 15. Switching loss comparison of IJ-ATMOS and C-ATMOS.

The majority of the process steps for HJD-ATMOS, including epitaxial growth, N+ source and P-well implantation, trench etching, P-base implantation, isolation oxidation, gate oxidation, polysilicon gate deposition, and metallization, are fully compatible with the manufacturing processes of C-ATMOS.

The N-channel region is formed by ion implantation at the bottom of the trench after trench etching. The split gate is formed by etching after trench oxidation, resulting in a thin layer of oxide between the gate and the P-Poly-Si. The gate-P-Poly-Si trench isolation layer is formed by thermal oxidation, and the trench oxide layer is fully etched and filled with P-Poly-Si.

Table 2 compares the HJD-ATMOS and the C-ATMOS in terms of their main characteristics. Dynamic FOM indicates the value of Ron,sp × Qgd. The HJD-ATMOS performs better due to the integrated HJD structure.

Table 2. Device characteristics comparison.

4. Conclusions

This paper proposes a novel asymmetric trench SiC MOSFET with a heterojunction diode. The performance of HJD-ATMOS and C-ATMOS is compared in detail. It can be observed that HJD-ATMOS demonstrates superior third-quadrant performance with a lower Vcut-in because of the integrated HJD. Compared with C-ATMOS, the Qgd of HJD-ATMOS has decreased by 31.91%. This is because the split gate design further reduces the total gate charge, which reduces the switching loss of the HJD-ATMOS device without affecting other key characteristics.

As a result, HJD-ATMOS eliminates bipolar degradation and reduces the turn-on loss from 0.69 mJ/cm2 in C-ATMOS to 0.26 mJ/cm2. With its advantageous features, HJD-ATMOS is a strong contender for power electronic applications.

Authors

Yiren Yu, Zijun Cheng, Yi Hu, Ruiyi Lv, Shengdong Hu.

Original – MDPI

-

LATEST NEWS / SiC / WBG2 Min Read

In the paper “Milliseconds Power Cycling (PCmsec) Driving Bipolar Degradation in Silicon Carbide Power Devices”, Sibasish Laha from Fraunhofer IISB and his co-authors Jürgen Leib, Andreas Schletz, Martin Maerz, Christian Liguda, Firas Faisal and Davood Momeni describe an innovative approach to silicon carbide (SiC) power cycling.

Until now, bipolar degradation (BD) tests have not been sufficiently differentiated in the investigation of failure and fault mechanisms for SiC power devices. SiC power products may experience voltage degradation which stems from the stacking faults (SFs) growth, commonly known as BD. To properly evaluate the BD impact on the electric performance of devices, it is important to distinguish it from other stress-related degradation such as power metal or interconnection.

This aspect has not yet been addressed, although the BD mechanism is well understood. The paper outlines a methodology by modifying the power cycling test (PCsec) to PCmsec in order to systematically investigate the effect of BD while controlling the impact of thermal degradation. This method enables a thorough evaluation of the distinct influences of both degradation contributors.

The complete paper will soon be available in the CIPS proceedings. Until then, feel free to download the paper presentation on event page.

There you can also find all our contributions to CIPS 2024:- Modified Approach for the Rainflow Counting Analysis of Temperature Load Signals in Power Electronics Modules – Oral presentation by S. Letz; Co-authors: D. Zhao, J. Leib, B. Eckardt, M. März

- Milliseconds Power Cycling (PCmsec) Driving Bipolar Degradation in Silicon Carbide Power Devices – Oral presentation by S. Laha; Co-authors: D. Momeni, J. Leib, A. Schletz, M. März, C. Liguda, F. Faisal

- Challenges of Junction Temperature Calibration of SiC MOSFETs for Power Cycling – a Dynamic Approach – Poster by J. Breuer, F. Dresel, A. Schletz, J. Klier, J. Leib, M. März, B. Eckardt

- Wide Bandwidth PCB Rogowski Coil Current Sensor with Droop Suppression and DC Restoration for In-Situ Inverter Measurements – Poster by S. Quergfelder, J. Sax, T. Heckel, B. Eckardt, M. März

Original – Fraunhofer IISB